Milad Darvishi

# ACTIVE N-PATH FILTERS: THEORY AND DESIGN

Milad Darvishi

#### The Graduation Committee:

Chairman and secretary:

Prof. dr. ir. A.J. Mouthaan University of Twente

Promoter:

Prof. dr. ir. B. Nauta University of Twente

Assistant promoter:

Dr. ir. Ronan van der Zee University of Twente

Members:

Prof. dr. ir. Frank van Vliet University of Twente/ TNO

Prof. dr. ir. William Scanlon University of Twente

Prof. Andreas Kaiser Lille Catholic University/ISEN

Prof. dr. ir. Arthur van Roermund Technical University of Eindhoven

This research is supported by the Dutch Technology Foundation STW, which is part of the Netherlands Organisation for Scientific Research (NWO) and partly funded by the Ministry of Economic Affairs (10048).

CTIT Ph.D. Thesis Series No. 13-263 Centre for Telematics and Information Technology P.O. Box 217, 7500 AE Enschede, The Netherlands

ISSN: 1381-3617(CTIT Ph.D. Thesis Series No. 13-263)

ISBN: 978-90-365-0542-0

DOI: http://dx.doi.org/10.3990/1.9789036505420

Copyright © 2013 by Milad Darvishi, Enschede, The Netherlands All rights reserved.

Typeset with LATEX.

This thesis was printed by Gildeprint Drukkerijen, The Netherlands.

# ACTIVE N-PATH FILTERS: THEORY AND DESIGN

#### DISSERTATION

to obtain the degree of doctor at the University of Twente, on the authority of the rector magnificus, prof. dr. H. Brinksma, on account of the decision of the graduation committee to be publicly defended on Wednesday  $25^{\rm th}$  September 2013 at 12:45

by

Milad Darvishi born on 19<sup>th</sup> September 1983 in Masjedsoleiman, Iran This dissertation has been approved by:

Promoter: Prof. dr. ir. B. Nauta

Assistant Promoter: Dr. ir. Ronan van der Zee

## Samenvatting

Radio-ontvangers hebben te maken met sterke signalen buiten de ontvangstband, welke bandfilters noodzakelijk maken. Op dit moment kan het grootste gedeelte van zendontvangers op chip geïntegreerd worden, maar ondanks tientallen jaren onderzoek is het nog steeds niet mogelijk kwalitatief goede banddoorlaatfilters mee te integreren. De lage kwaliteit van geïntegreerde spoelen zorgt voor filters met grote verliezen, een klein dynamisch bereik en lage onderdrukking in de stopband. Om deze redenen gebruiken de meeste draadloze systemen tegenwoordig discrete filters naast de chip, wat hogere kosten en een groter volume met zich meebrengt. Dit wordt verergert doordat moderne draadloze apparatuur vaak vele draadloze standaarden moet ondersteunen, hetgeen tot een veelheid aan externe filters leidt.

Banddoorlaatfilters gebaseerd op G<sub>m</sub>-C filters en op LC filters met verbeterde kwaliteitsfactor zijn niet in staat goede specificaties te combineren met een grote verstembaarheid. N-path filters, daarentegen, bieden deze mogelijkheid wel doordat de frequentie van de doorlaatband wordt bepaald door een klokfrequentie en de bandbreedte door de waarde van capaciteiten. N-path filters zijn opgebouwd uit voornamelijk schakelaars, capaciteiten en digitale elektronica. Hierdoor kunnen ze uitstekend in CMOS processen gerealiseerd worden, ook als de afmetingen van deze processen in de toekomst verder afnemen. Dit proefschrift onderzoekt daarom banddoorlaatfilters gebaseerd op deze N-path techniek, waarvan er verscheidene zijn ontworpen en gerealiseerd.

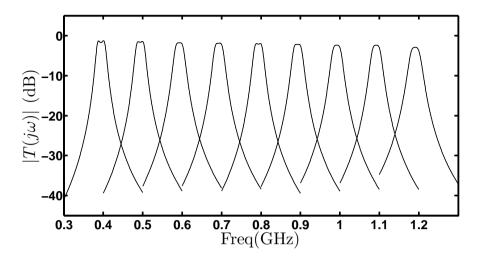

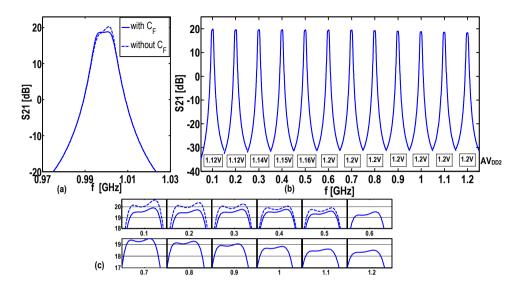

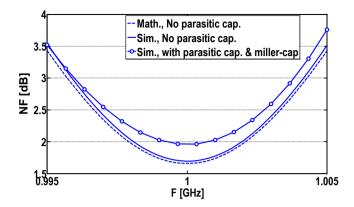

De maximale onderdrukking in traditionele N-path filters wordt beperkt door de weerstand van de schakelaars. In dit proefschrift wordt een 4° orde banddoorlaat filter geïntroduceerd dat is gebaseerd op het verschil tussen twee 2° orde filters met iets verschillende centrum-frequentie, mogelijk gemaakt door een  $G_m$ -C techniek. Dit filter elimineert het effect van de weerstand van de schakelaars op de maximale onderdrukking in de stopband. Het filter is gerealiseerd in 65 nm CMOS. De metingen laten zien dat dit filter een stopbandonderdrukking van meer dan 55 dB heeft, 40 dB meer dan conventionele N-path filters, en een betere vorm van de doorlaatband. IIP3 in de doorlaatband is +9 dBm, en in de stopband ( $\Delta f = 50 \text{ MHz}$ ) +29 dBm. De centrumfrequentie is instelbaar van 0.4 GHz tot 1.2 GHz.

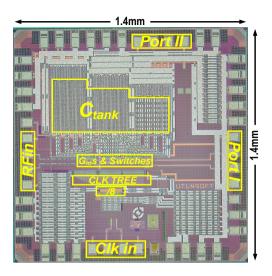

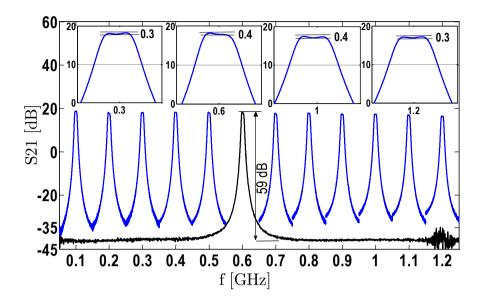

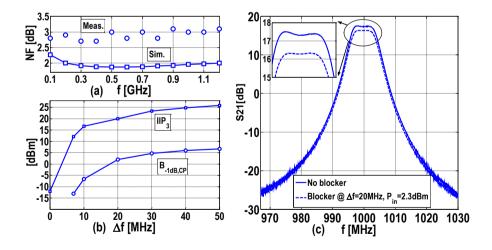

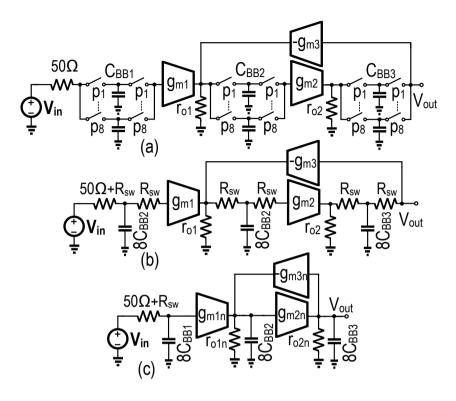

Vervolgens wordt een ontwerpmethode voorgesteld voor de synthese van actieve N-path filters. Om deze methode te verifiëren is een 6° orde 8-pad RF filter in 65 nm CMOS gerealiseerd. Dit filter haalt 59 dB stopbandonderdrukking, 25 dB versterking en een rimpel van < 0.6 dB in de doorlaatband. De versterking helpt om de eisen aan de ruis in de volgende trappen van de ontvanger te vergemakkelijken. Het filter dankt de goede vorm van de doorlaatband aan het gebruik van een Miller-compensatie methode. IIP3 in de doorlaatband is -12 dBm, en in de stopband ( $\Delta f = 50$  MHz) +26 dBm. Het 1 dB compressiepunt voor interferentie op  $\Delta f = 50$  MHz ligt op +7 dBm. Dit filter heeft een ruisgetal van 2.8 dB. Dit is bijna 7 dB lager dan dat van het vorige filter, voornamelijk te danken aan het feit dat de  $G_{\rm m}$  cellen nu op RF frequenties werken en dus minder last hebben van 1/f ruis. De centrum-frequentie is instelbaar van 0.1 GHz tot 1.2 GHz en de bandbreedte is 8 MHz. Het filter bestaat uitsluitend uit inverters, schakelaars en capaciteiten en is dus goed schaalbaar naar kleinere CMOS technologieën.

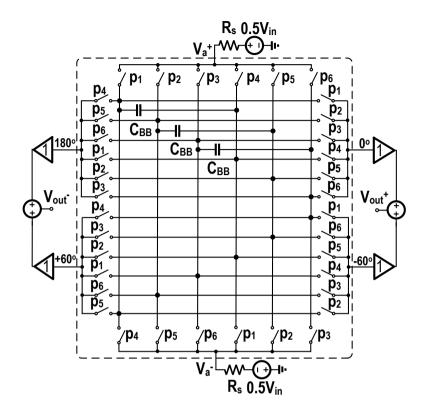

Tenslotte wordt een techniek voorgesteld om de banddoorlaat-eigenschappen van een 6-pad filter op de 2e en 3e harmonische van de klokfrequentie te onderdrukken. Eén van de problemen van N-path filters is de herhaling van de banddoorlaat-karakteristiek op hogere harmonischen van de klokfrequentie. Interferentie op deze frequenties wordt met weinig verzwakking doorgelaten en vermindert de gevoeligheid van de ontvanger achter het filter. Simulaties in 28 nm FDSOI laten zien dat een 3e harmonische onderdrukking van 40 dB mogelijk is. Ook wordt een methode geïntroduceerd waarmee het mogelijk is de overdracht van N-path filters over een groot frequentiebereik uit te rekenen op een aanzienlijk eenvoudiger manier dan tot dusver uit de literatuur bekend is. Met deze methode kan ook het effect van parasitaire capaciteiten op een intuïtieve en eenvoudige manier gevonden worden.

## Abstract

Nowadays, wireless devices cover numerous wireless communication standards where almost for each one, a different frequency band has been allocated. There is a strong motivation towards SoC (System-on-Chip) solutions, where everything is integrated inside a chip to reduce the cost and form-factor of wireless devices. In radio-frequency receivers, due to the existence of large out-of-band blockers and a limited dynamic range, band-select filtering of the input signal is essential. Currently, most of the front-end circuitry of transceivers can be integrated on-chip. However, it is not possible to build integrated high-performance bandpass filters even after more than a decade research on this very topic. The inherent losses associated with on-chip inductors lead to filters having relatively high insertion losses, limited dynamic range and low out-of-band rejection. For this reason, nowadays, most wireless systems utilize individual off-chip filters rather than fully integrated bandpass filters. This increases the size and cost. Moreover, most current wireless devices have several standards which leads to the exploitation of numerous off-chip bandpass filters which further exacerbate the size and cost issues.

Although G<sub>m</sub>-C and Q-enhanced LC RF bandpass filters are not capable to deliver high performance and wideband tunablitiy, N-path bandpass filters are. N-path filters are old and were forgotten. N-path filters can provide us with bandpass filters having high Q-factors and wide center-frequency tuning range. The center frequency of the N-path bandpass filter is set by its clock frequency and its bandwidth is determined by the value of its capacitors and source resistance. The principal constituents of N-path filters are switches, capacitors and a digital circuitry for providing clock signals needed for the operation of these filters. CMOS technology can offer very linear switches, high density capacitors and very fast digital gates. Therefore, CMOS technology is the best candidate for the implementation of N-path bandpass filters which are friendly with process scaling. Consequently, this thesis investigates the possibilities of RF bandpass filters with high selectivity, high dynamic range and wide center-frequency tuning range based on N-path filter technique. In this thesis, several bandpass filters based on N-path technique have been designed and implemented.

The ultimate rejection of classical N-path filters is limited due to a non-zero switch

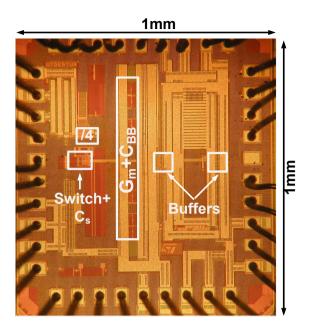

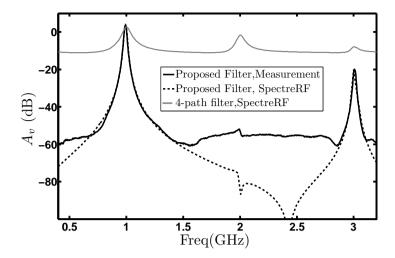

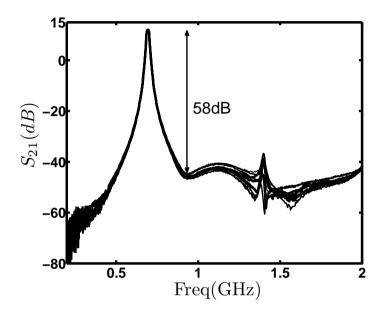

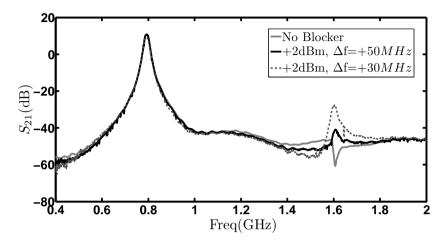

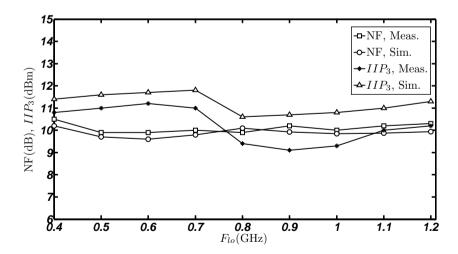

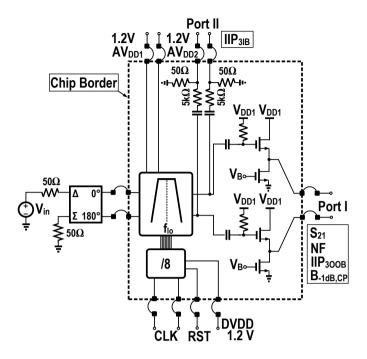

resistance. A widely tunable 4<sup>th</sup> order bandpass filter based on the subtraction of two 2<sup>nd</sup> order 4-path filters having a second set of switches with slightly different center frequencies, generated by a  $G_m$ -C technique, is proposed. This filter eliminates the effect of switch resistance on the stopband rejection of the filter. As a proof of concept, this filter is implemented in CMOS LP 65 nm. Measurement results demonstrate that this filter achieves > 55 dB stopband rejection (40 dB better than conventional N-path filters) and better passband shape compared to conventional N-path filters. The in-band and out-of-band IIP3 of the filter are +9 dBm and +29 dBm ( $\Delta f = 50$  MHz), respectively. The center frequency of the filter is tunable from 0.4 GHz to 1.2 GHz.

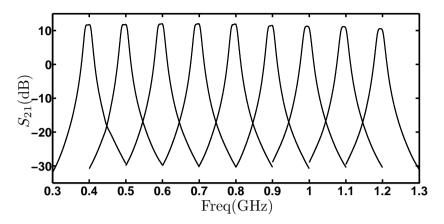

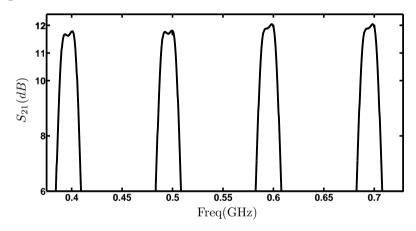

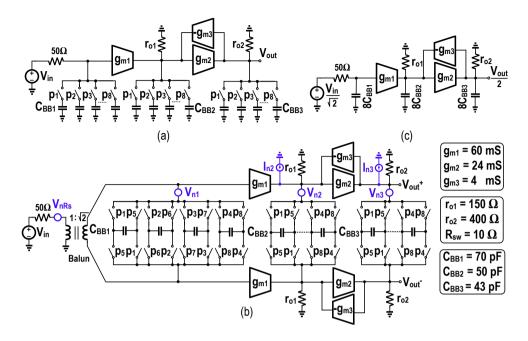

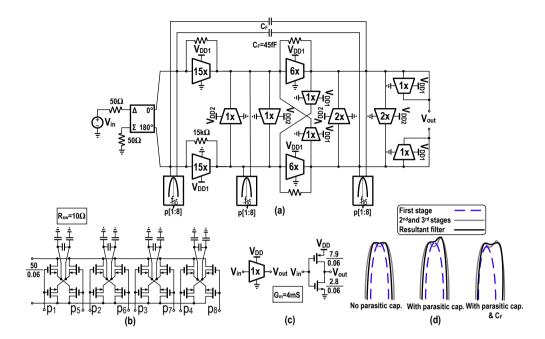

Afterwards, a design methodology for synthesis of general active N-path bandpass filters is proposed. To verify the theory, a tunable 6<sup>th</sup> order 8-path RF channel-select filter in CMOS LP 65 nm is introduced. The filter achieves a stopband rejection of +59 dB, passband gain of +25 dB and passband ripples < 0.6 dB. In this way, while the blockers are eliminated by filtering, the passband gain of the filter relaxes the noise requirement of the following stages in the receiver. The proposed filter achieves a good passband shape thanks to utilizing a Miller compensation method. The inband and out-of-band IIP3 of the filter are -12 dBm and +26 dBm ( $\Delta f = 50$  MHz), respectively. The filter is capable of obtaining 1dB blocker compression point of +7 dBm ( $\Delta f = 50 \text{ MHz}$ ). This filter has an average noise figure of 2.8 dB which is almost 7 dB better than our previous work. Compared to the previous proposed filter, this filter can achieve lower noise figure due to the exploitation of G<sub>m</sub> cells in RF frequency instead of IF frequency. The center frequency of the filter is tunable from 0.1 GHz to 1.2 GHz and the bandwidth of the filter is 8 MHz. The proposed filter only consists of inverters, switches and capacitors and therefore it is friendly with process scaling. This filter defines the state-of-the-art of RF BPFs.

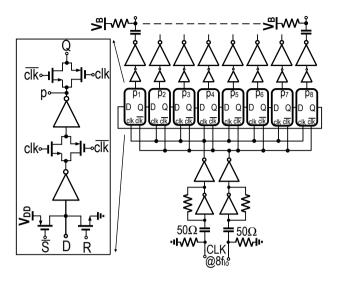

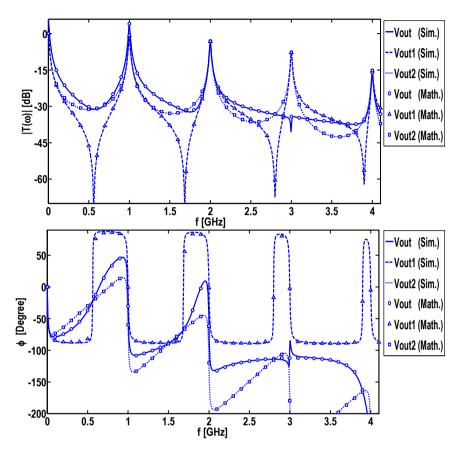

Finally, a technique to concurrently eliminate the bandpass shapes at second and third harmonics of clock frequency of a 6-path filter is proposed. One of the issues of N-path filters is the repetition of the bandpass shapes at higher harmonics of the clock frequency. Blockers located at these frequencies, that are passed with less attenuation, can degrade the sensitivity of a receiver that comes after the filter. Simulations in CMOS 28 nm FDSOI show the possibility of obtaining a third harmonic rejection of 40 dB. Moreover, a compact method to calculate the transfer function of N-path filters over a large frequency range is introduced which avoids the lengthy analysis presented in literature so far and also through a simple and intuitive method, the effect of parasitic capacitance on the performance of N-path filters is found.

## Contents

| Sa       | Samenvatting |                                                                              |    |  |  |  |  |  |  |  |

|----------|--------------|------------------------------------------------------------------------------|----|--|--|--|--|--|--|--|

| Abstract |              |                                                                              |    |  |  |  |  |  |  |  |

| 1        | Intr         | Introduction                                                                 |    |  |  |  |  |  |  |  |

|          | 1.1          | Wireless Transceivers                                                        | 1  |  |  |  |  |  |  |  |

|          | 1.2          | Motivation                                                                   | 2  |  |  |  |  |  |  |  |

|          | 1.3          | Thesis Outline                                                               | 5  |  |  |  |  |  |  |  |

| 2        | App          | approaches to Integrated Analog Bandpass Filters                             |    |  |  |  |  |  |  |  |

|          | 2.1          | Introduction                                                                 | 7  |  |  |  |  |  |  |  |

|          | 2.2          | Q-enhanced LC BPF                                                            | 8  |  |  |  |  |  |  |  |

|          |              | 2.2.1 Operation                                                              | 8  |  |  |  |  |  |  |  |

|          |              | 2.2.2 Performance                                                            | 9  |  |  |  |  |  |  |  |

|          |              | 2.2.3 Frequency Response Stability                                           | 12 |  |  |  |  |  |  |  |

|          | 2.3          | $G_m$ -C BPFs                                                                | 13 |  |  |  |  |  |  |  |

|          |              | 2.3.1 Operation                                                              | 13 |  |  |  |  |  |  |  |

|          |              | 2.3.2 Performance                                                            | 15 |  |  |  |  |  |  |  |

|          |              | 2.3.3 Frequency Response Stability                                           | 16 |  |  |  |  |  |  |  |

|          | 2.4          | Micro-Mechanical Filters                                                     | 17 |  |  |  |  |  |  |  |

|          |              | 2.4.1 Piezoelectric Resonators                                               | 18 |  |  |  |  |  |  |  |

|          |              | 2.4.2 Capacitive-Transduction Resonators                                     | 19 |  |  |  |  |  |  |  |

|          | 2.5          | N-path Filters                                                               | 24 |  |  |  |  |  |  |  |

|          | 2.6          | Conclusion                                                                   | 26 |  |  |  |  |  |  |  |

| 3        | Tur          | Tunable Switched G <sub>m</sub> -C Bandpass Filter Based on N-path Filters 2 |    |  |  |  |  |  |  |  |

|          | 3.1          | Introduction                                                                 | 27 |  |  |  |  |  |  |  |

|          | 3.2          | Increasing BPF Order By Subtraction                                          |    |  |  |  |  |  |  |  |

|          | 3.3          | Shifting the center frequency of a 4-path filter                             | 31 |  |  |  |  |  |  |  |

|          | 3.4          | Splitting the input signal                                                   | 36 |  |  |  |  |  |  |  |

|   |     | 3.4.1                                                                                   | The effect of series capacitor on a conventional 4-path filter         | 38       |  |  |  |  |  |  |  |

|---|-----|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------|--|--|--|--|--|--|--|

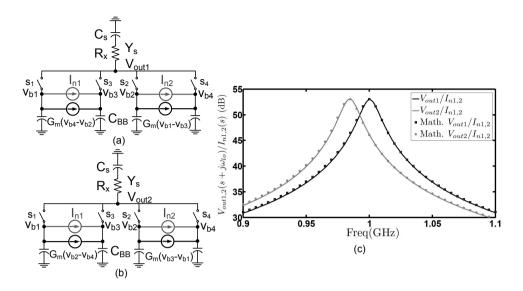

|   |     | 3.4.2                                                                                   | Transfer function of the implemented filter                            | 38       |  |  |  |  |  |  |  |

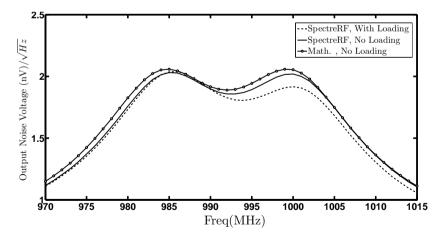

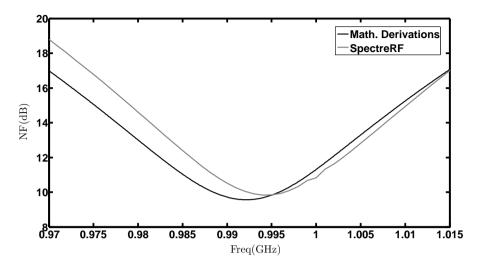

|   |     | 3.4.3                                                                                   | NF of the implemented filter                                           | 42       |  |  |  |  |  |  |  |

|   | 3.5 | Realiz                                                                                  | ation                                                                  | 44       |  |  |  |  |  |  |  |

|   | 3.6 | Measurements                                                                            |                                                                        |          |  |  |  |  |  |  |  |

|   | 3.7 | Conclusions                                                                             |                                                                        |          |  |  |  |  |  |  |  |

|   | 3.A | An N-                                                                                   | path Filter with Generic Source and Baseband Impedances                | 54       |  |  |  |  |  |  |  |

|   | 3.B | Addit                                                                                   | ion of a Series Capacitor to the Source Impedance of a 4-path          |          |  |  |  |  |  |  |  |

|   |     | Filter                                                                                  |                                                                        | 56       |  |  |  |  |  |  |  |

|   | 3.C | NF Ca                                                                                   | alculation of the Implemented Filter                                   | 58       |  |  |  |  |  |  |  |

| 4 | Des | Design of Active N-path Filters 61                                                      |                                                                        |          |  |  |  |  |  |  |  |

|   | 4.1 | Introd                                                                                  | luction                                                                | 61       |  |  |  |  |  |  |  |

|   | 4.2 | High-o                                                                                  | order Active N-path Filters                                            | 62       |  |  |  |  |  |  |  |

|   |     | 4.2.1                                                                                   | Compact Analysis of Conventional N-path filters                        | 63       |  |  |  |  |  |  |  |

|   |     | 4.2.2                                                                                   | Design Methodology of Higher Order N-path Filters                      | 66       |  |  |  |  |  |  |  |

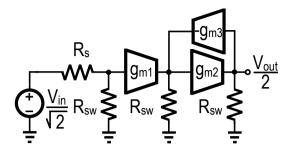

|   |     | 4.2.3                                                                                   | The Effect of Switch Resistance on N-path Filters                      | 67       |  |  |  |  |  |  |  |

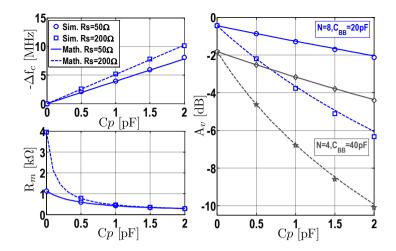

|   |     | 4.2.4                                                                                   | The Effect of Parasitic Capacitance on N-path Filters                  | 69       |  |  |  |  |  |  |  |

|   | 4.3 | Design                                                                                  | n of the Proposed Filter                                               | 73       |  |  |  |  |  |  |  |

|   |     | 4.3.1                                                                                   | Transfer Function of the Filter                                        | 73       |  |  |  |  |  |  |  |

|   |     | 4.3.2                                                                                   | NF of the Filter                                                       | 76       |  |  |  |  |  |  |  |

|   | 4.4 | Realiz                                                                                  | ation                                                                  | 78       |  |  |  |  |  |  |  |

|   |     | 4.4.1                                                                                   | Simulation Results                                                     | 82<br>83 |  |  |  |  |  |  |  |

|   | 4.5 | Measurements                                                                            |                                                                        |          |  |  |  |  |  |  |  |

|   | 4.6 | Conclusion                                                                              |                                                                        |          |  |  |  |  |  |  |  |

|   | 4.A |                                                                                         | ding Two N-path Filters                                                | 88       |  |  |  |  |  |  |  |

|   | 4.B | Elimination of the Effect of $\mathbf{R}_{sw}$ on Ultimate-Rejection of the Filter . 89 |                                                                        |          |  |  |  |  |  |  |  |

| 5 | Sup | _                                                                                       | ng Harmonic Responses in N-path Filters                                | 91       |  |  |  |  |  |  |  |

|   | 5.1 |                                                                                         | luction                                                                | 91       |  |  |  |  |  |  |  |

|   | 5.2 | Elimir                                                                                  | nation of Bandpass Shapes at Higher Harmonics of $f_{lo}$              | 94       |  |  |  |  |  |  |  |

|   |     | 5.2.1                                                                                   | An N-path Filter with Large Stopband Rejection                         | 94       |  |  |  |  |  |  |  |

|   |     |                                                                                         | Elimination of Bandpass Shapes at $3f_{lo}$                            | 96       |  |  |  |  |  |  |  |

|   |     | 5.2.3                                                                                   | Compact Analysis of an N-path Filter with Second Set of Switches       |          |  |  |  |  |  |  |  |

|   |     | 5.2.4                                                                                   | Concurrent Suppression of Bandpass Shapes at $2f_{lo}$ and $3f_{lo}$ . | 100      |  |  |  |  |  |  |  |

|   | 5.3 |                                                                                         | -Matching and Amplification                                            | 103      |  |  |  |  |  |  |  |

|   |     | 5.3.1                                                                                   | Input-Matching                                                         | 103      |  |  |  |  |  |  |  |

|   |     | 5.3.2                                                                                   | Transfer Function of the Modified Filter                               | 106      |  |  |  |  |  |  |  |

|   |     | 5.3.3                                                                                   | Stability of the Filter                                                | 108      |  |  |  |  |  |  |  |

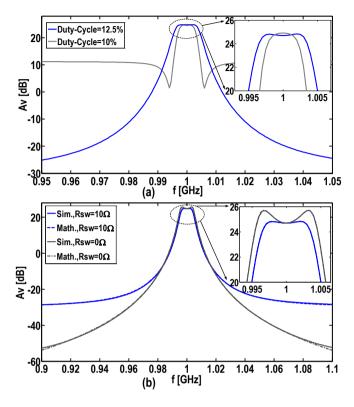

|   | 5.4 | Circui                                                                                  | it Simulations in CMOS 28 nm FDSOI                                     | 108      |  |  |  |  |  |  |  |

|                                                                         |                      | 5.4.1 The effect of Parasitic Capacitance on the Filter $\dots \dots$ | 110 |  |  |  |  |

|-------------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------|-----|--|--|--|--|

|                                                                         |                      | 5.4.2 Transfer Function, NF and IIP <sub>3</sub> Simulations          | 112 |  |  |  |  |

| 5.5 Conclusions                                                         |                      |                                                                       |     |  |  |  |  |

|                                                                         | 5.A NF of the Filter |                                                                       |     |  |  |  |  |

| 5.B The Effect of Parasitic Capacitance on N-path Filters $\dots \dots$ |                      |                                                                       |     |  |  |  |  |

| 6                                                                       | Conclusions          |                                                                       |     |  |  |  |  |

|                                                                         | 6.1                  | Summary and Conclusions                                               | 121 |  |  |  |  |

|                                                                         | 6.2                  | Original Contributions                                                | 122 |  |  |  |  |

|                                                                         | 6.3                  | Future Work                                                           | 123 |  |  |  |  |

| A                                                                       | Acknowledgement      |                                                                       |     |  |  |  |  |

| Bi                                                                      | Bibliography         |                                                                       |     |  |  |  |  |

| List of publications                                                    |                      |                                                                       |     |  |  |  |  |

| Bi                                                                      | Biography            |                                                                       |     |  |  |  |  |

## Chapter 1

### Introduction

#### 1.1 Wireless Transceivers

Nowadays, wireless communication is an indispensable part of our life. Standards like GSM, WCDMA and EDGE are devoted to voice and data communications. Navigation has become equivalent to using GPS. Thanks to WLAN, a fast wireless Internet and peer-to-peer connections are available. Bluetooth empowers low power and short range connectivity between different devices. Near Field Communication (NFC) is an emerging standard that targets applications such as contactless transaction and data exchange. It is quite intriguing to have all the above mentioned services in a small cell-phone. Mobile phone technology has come a long way since the first mobile phone call was made 40 years ago [2]. If we compare the first available mobile phone with a recent one, there is a huge difference between their size, cost, power consumption and functionality. This is mainly due to: 1) the scaling of VLSI processes, particularly CMOS technology, and 2) innovations in RF architectures, circuits and devices [3]. In fact, the minimum feature size of CMOS technology has fallen from 5  $\mu$ m in 1972 [4] to 19 nm in 2013 [5].

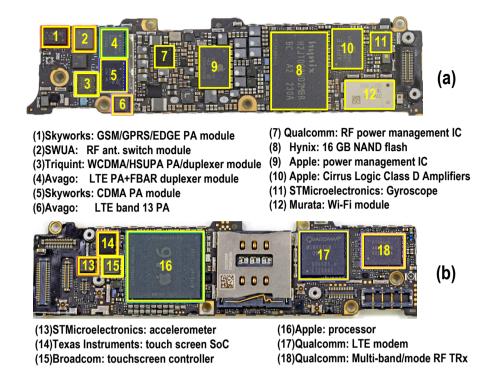

The first mobile phone (Motorola DynaTAC) [2] was 23 cm tall, comprised 30 circuit boards, had a talk-time of 35 minutes, took 10 hours to recharge and had a price of 3,995 \$. The first mobile phone and a modern one (Apple iphone 5) are illustrated in Fig. 1.1 for a comparison. To demonstrate the sophistication of current mobile phones, the circuit board of the latter is shown in Fig. 1.2. As can be seen, the two sides of the PCB have been fully filled in with numerous ICs from different manufacturers.

<sup>&</sup>lt;sup>1</sup>In contrast, Martin Cooper, the inventor of the first mobile phone, says: "They (cell-phones) all try to be universal. If you try to build a device that does all the things for all people, it will not do any of them very well. So i think that is where we are with cell-phones today"[1].

Figure 1.1: (a) The first mobile phone made by Motorola (DynaTAC) (b) The latest smart phone made by Apple (iphone 5).

#### 1.2 Motivation

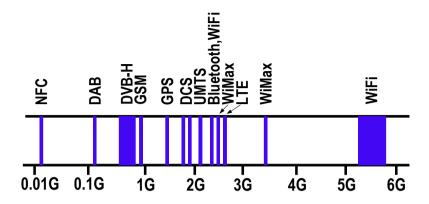

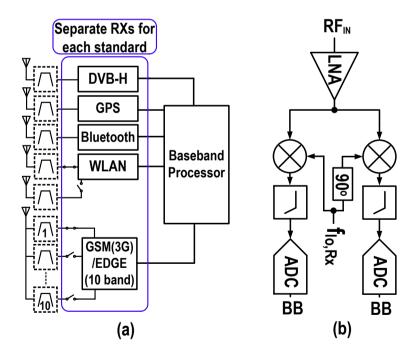

Almost each previously mentioned wireless standard occupies a different frequency band. Fig. 1.3 demonstrates the frequency bands allocated to different wireless standards. A generic multi-standard receiver and the block diagram of a typical receiver are illustrated in Fig. 1.4(a) and Fig. 1.4(b), respectively. As can be seen, copious amount of off-chip bandpass filters (BPF) are used. These BPFs are off-chip, bulky and expensive and hence increase the cost and form-factor. One approach to reduce the form-factor and size of wireless devices is to use SiP (System-in-Package) solutions where a BPF fabricated in a piezoelectric substrate and a CMOS transceiver chip are stacked together inside a package [7]. As an example, see parts 3, 4, 12 and 18 in Fig. 1.2. To further reduce the cost and form-factor of wireless devices, there is a strong motivation towards SoC (System-on-Chip) solutions, where everything is integrated inside a chip. Therefore, it is interesting to come up with solutions that eliminate the demand for off-chip BPFs. Two possible options are: 1) come up with novel circuits and receiver architectures that do not require these BPFs; and 2)

Figure 1.2: The circuit board of a modern smart phone (iphone 5) [6]: (a) The upper side of PCB (b) The lower side of PCB.

substitute these off-chip filters with integrated ones.

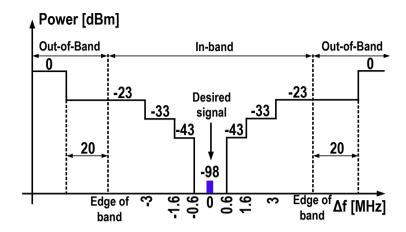

These off-chip BPFs considerably attenuate large undesired signals, located outside the band of interest, and hence ease the detection of desired signals. As an example, the in-band and out-of-band GSM receiver blocking level test is depicted in Fig. 1.5. This figure implies that the GSM receiver should cope with out-of-band blockers with  $P_b = 0$  dBm while successfully detecting a desired signal with power level of -98 dBm. Without filtering, this 98 dB of difference, is quite difficult to handle.<sup>2</sup> Therefore, the first option seems to be rather impractical.

The second option is to substitute off-chip BPFs with integrated ones. In this thesis, we will focus on exploring methods for designing integrated RF BPFs with large out-of-band signal-handling capabilities without sacrificing the sensitivity of the

<sup>&</sup>lt;sup>2</sup>A typical off-chip BPF for GSM band can be found in [8]. Usually, the amount of required rejection is found by the fact that the effective strength of undesired out-of-band signals should be at most equal to the largest in-band interferer. For example, in GSM standard, the pre-filter should provide at least 23 dB of rejection for 0 dBm undesired signals.

Figure 1.3: Frequency band allocations of different wireless standards used in mobile phones.

Figure 1.4: (a) A generic multi-standard receiver where each standard has a separate receiver (b) A block diagram of typical receivers used in (a).

Figure 1.5: GSM receiver blocking test [3]. (The desired channel center frequency is denoted by 0 for simplicity).

receiver that comes after it. Also, these filters should have high selectivity, and wide center-frequency tuning range to cover different frequency-bands and save area.

#### 1.3 Thesis Outline

In *chapter 2*, a summary of different approaches to the integration of RF BPFs will be given. Issues such as frequency response stability, high-frequency performance, signal-handling capability, noise and power dissipation will be addressed for each approach. Accordingly, the choice for N-path filters will be motivated.

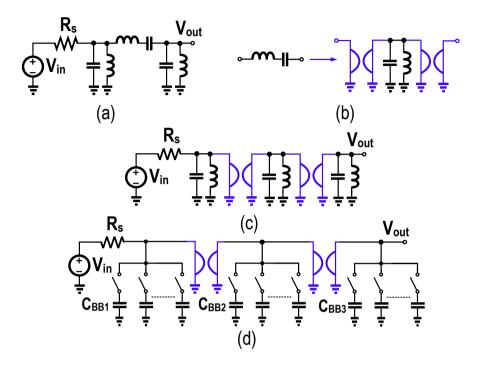

In chapter 3,4 and 5, several BPFs are designed based on the N-path filter technique. In chapter 3, a widely tunable  $4^{\rm th}$  order BPF based on the subtraction of two  $2^{\rm nd}$  order 4-path filters with slightly different center frequencies, generated by a  $G_{\rm m}$ -C technique, is proposed. This filter achieves larger stopband rejection and better passband shape compared to conventional N-path filters.

In chapter 4, a widely-tunable and highly-selective filter with a decent amount of embedded amplification is introduced. In this way, while the blockers are eliminated by filtering, the passband gain of the filter relaxes the noise requirement of the following stages in the receiver. Furthermore, the design methodology for synthesis of active N-path BPF is introduced. Based on this methodology, a tunable 6<sup>th</sup> order 8-path RF channel-select filter is introduced. It is based on coupling N-path filters with gyrators, achieving a "flat" passband shape and high out-of-band linearity. A technique is utilized to considerably improve the passband shape of the filter. The proposed filter only consists of inverters, switches and capacitors and therefore it is

friendly with process scaling. Compared to the filter technique introduced in *chapter* 3, this filter can achieve lower noise figure due to the exploitation of  $G_m$  cells in RF frequency instead of IF frequency.

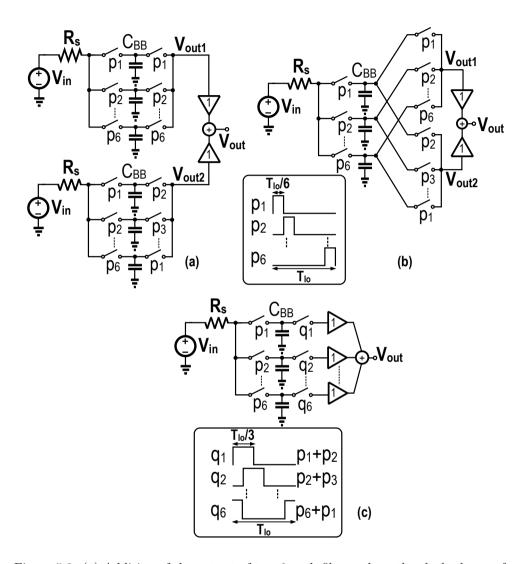

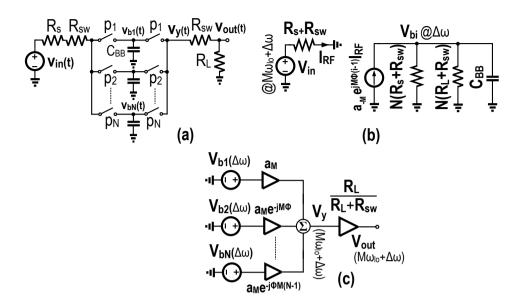

In chapter 5, a technique to concurrently eliminate the bandpass shapes at second and third harmonics of a 6-path filter is proposed. In conventional N-path filters, blockers located at the second and third harmonics of the clock frequency are passed which can degrade the sensitivity of a receiver that comes after the filter. Moreover, a compact method to calculate the transfer function of N-path filters over a large frequency range is introduced which avoids the lengthy analysis presented in literature so far and through a simple and intuitive method, the effect of parasitic capacitance on the performance of N-path filters is found.

In *chapter* 6, conclusions and an overall summary of the thesis will be given. Moreover, the original contributions will be pointed out and some directions for future research will be proposed.

## Chapter 2

## Approaches to Integrated Analog Bandpass Filters

#### 2.1 Introduction

Wireless communication systems continue to evolve, supporting multiple standards while facilitating a growing number of portable wireless devices operating in a common frequency spectrum. The success of commercial wireless communication products is due, in part, to the inclusion of highly integrated radio frequency (RF) transceivers which feature low cost, low power consumption, and performance levels that meet demanding system specifications. The architecture of integrated RF transceivers has been largely determined by RF bandpass filter performance and system requirements [9]. Early radio architectures such as super-heterodyne needed several bandpass filters (BPF) in the receiver or transmitter chain to suppress interference and image signals. These filters were typically off-chip, bulky and expensive which led to penalties in terms of cost, form factor and less design flexibility. The push towards single-chip solutions led to a tremendous amount of research on the integration of these bandpass filters [9, 10, 11, 12, 13, 14, 15, 16]. Analog BPFs have been notoriously difficult to implement on-chip. Due to the lack of success in implementation of RF BPFs having both high DR and high Q-factor, designers explored other possible architectural solutions such as zero- or low-IF receivers where the amount of required bandpass filtering is much lower compared to conventional heterodyne receivers [17]. These types of receivers have to cope with other issues such as 1/f noise, LO self-mixing, DC offsets and etc. [3]. However, these issues have been alleviated through extensive digital calibrations [3]. One remaining issue that has not been resolved is the fundamental limitation on the DR of the direct-conversion receivers. By moving all the channelselect filtering to the baseband sections, the low-noise amplifier (LNA) which should have sufficient gain is subjected to the full RF spectrum. Thus, strong out-of-band and out-of-channel blockers can severely desensitize the receiver. Therefore some preselect filtering is required before the LNA which nowadays is typically done using off-chip BPFs such as surface acoustic wave (SAW) filters. The possibility of improving the DR of the receiver by removing the LNA and the BPF from the receiver chain has been proposed in [18, 19]. However, these type of receivers (mixer-first receiver) are quite power hungry for achieving the desired sensitivity and this issue exacerbates with down-scaling of the technology. Thus, the need for high-frequency, high-Q BPFs can not be eliminated. In this chapter, a summary of different approaches to the design of integrated BPFs will be given. Moreover, issues such as frequency response stability, high-frequency performance, signal-handling capability, noise and power dissipation will be addressed for each approach.

#### 2.2 Q-enhanced LC BPF

Integrated RF filters based on LC topologies exhibit poor performance because onchip inductors have low quality factors. The effects of the limited Q-factor of on-chip inductors in multi-pole BPFs are namely a significant drop in the insertion loss of the filter and a considerable reduction in the shape-factor of the filter ("shoulder droop") [20]. Obtaining a near ideal bandpass response requires inductors with quality factors of approaching 200 or more [21]. In fact, for the same bandwidth, as the order of the filter increases, the minimum tolerable Q-factor of inductors increases very rapidly [20]. The best available monolithic inductor in silicon substrate achieves Q-factors in the range of 10-30 depending on inductance value and frequency [21]. Clearly, some form of enhancement is required to make viable integrated RF LC BPFs.

#### 2.2.1 Operation

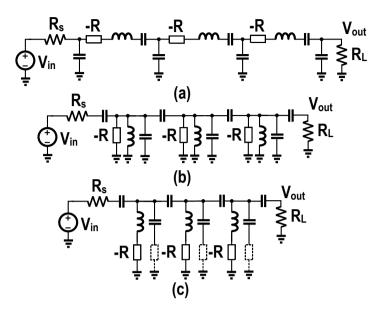

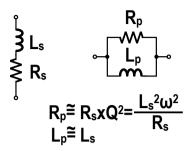

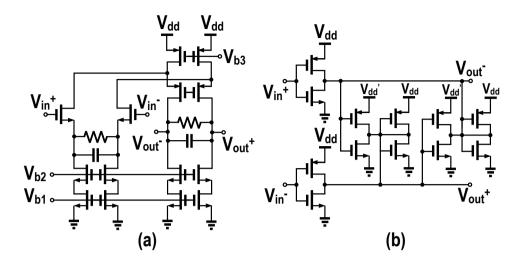

The two most popular topologies that have been utilized in integrated BPF design are series-C coupled resonators and shunt-C coupled resonators as illustrated in Fig. 2.1 [22]. These BPFs have the least spreads in their component values and moreover use a low number of inductors [22]. Conventionally a negative resistance is exploited to cancel the losses associated with monolithic inductors. As can be seen in Fig. 2.1, the negative resistance can be located in series or in parallel with the inductor. The location and the type of the negative resistance have a great impact on the passband distortion of Q-enhanced BPFs [16, 20, 21, 23, 24]. A very first-order model of an on-chip inductor where only the series ohmic loss is taken into account is shown in Fig. 2.2. Using narrowband approximations, a series RL can be converted to a parallel one [25] as depicted in Fig. 2.2. As can be seen, the parallel resistance,  $R_p$ , is a strong

Figure 2.1: (a) Shunt-C coupled resonator BPF using series negative resistance to cancel the loss of inductors (b) Series-C coupled resonator BPF utilizing parallel negative resistance (c) Series-C coupled resonator BPF utilizing series negative resistance with either inductor or capacitor.

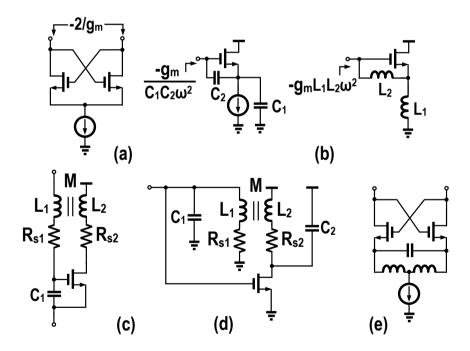

function of frequency. Here, we should make a critical observation. If a series negative resistance is used, it should not have frequency dependency and if a parallel one is exploited, it should have the same dependency on frequency as  $R_p$  does. Deviation from these rules will lead to a distortion in the passband shape of the filter [23]. Different types of negative resistors that have been used in Q-enhanced LC BPFs are shown in Fig. 2.3.

#### 2.2.2 Performance

While many definitions of DR exist, a simple and useful one in comparing different circuits is:

$$DR = \frac{P_{1dB}}{P_n} \tag{2.1}$$

where  $P_{1dB}$  is the 1-dB output compression power and  $P_n$  is the output noise floor [14]. It can be shown that the DR of a 2<sup>nd</sup> order Q-enhanced LC BPF shown in Fig. 2.4 is:

Figure 2.2: A first-order model of an on-chip inductor where the series ohmic loss is taken into account and its parallel counterpart.

Figure 2.3: Different types of negative resistors: (a) A constant and differential one (b) Frequency dependent negative resistors [16] (c) A series LC tank with a constant series negative resistance [20] (d) A parallel LC tank with a constant negative resistance in series with its inductor [21] (e) A modified differential negative resistance [21, 24].

Figure 2.4: A typical  $2^{nd}$  order Q-enhanced LC BPF

$$DR_{QELC} = \frac{\eta P_{DC}}{4kT(1+\gamma)B} \times \left(\frac{Q_0}{Q}\right)^2$$

(2.2)

Where  $\eta$  is the efficiency of the circuit, B is the bandwidth of the filter,  $\gamma$  is the noise excess factor of the  $G_m$  cells,  $Q_0$  is the uncompensated Q-factor of the inductor and Q is the Q-factor of the filter [14]. (2.2) tells us that increasing the raw quality factor of on-chip inductors has a great impact on the dynamic range of Q-enhancement filters [26, 27]. The DR of an LNA can be described by:

$$DR_{LNA} = \frac{\eta P_{DC}}{kTFGB}$$

(2.3)

where F is the noise factor, B is the bandwidth and G is the power gain of the LNA. By comparing (2.2) and (2.3), it can be deduced that to achieve a DR similar or better than an LNA, we should have:

$$Q_0 \ge 2Q\sqrt{\frac{1+\gamma}{\text{FG}}}\tag{2.4}$$

For example<sup>1</sup>, if F = 2 dB and G = 18 dB,  $Q/Q_0$  of up to 3 is theoretically permissible [14]. The linearity and the noise performance of the filter is limited by the negative resistance. In fact, the addition of the negative resistance: 1) modifies the  $P_{1dB}$  of the circuit to  $P_{1dB}Q_0/Q$  and 2) modifies the  $P_n$  of the circuit to  $P_nQ/Q_0$ . Although there has been more than a decade research on these types of BPFs, most of the designs do not achieve enough DR which is to a first degree is due to the limited Q-factor of on-chip inductors [9, 10, 11, 12, 13, 14, 15, 16, 20, 21, 23, 24, 26, 27, 28, 29, 30, 31, 32, 33].

<sup>&</sup>lt;sup>1</sup>Values in (2.4) are not in dB.

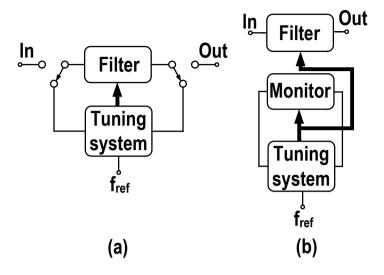

Figure 2.5: Automatic tuning: (a) Direct (b) Indirect.

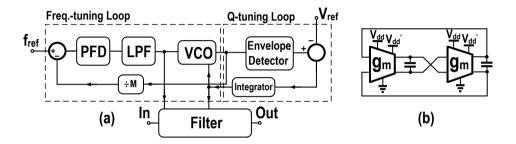

#### 2.2.3 Frequency Response Stability

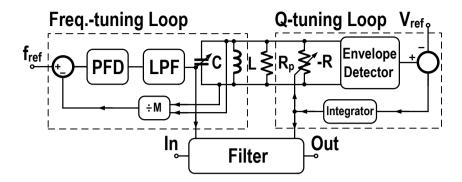

In general, fabrication tolerances and temperature variations can modify the transfer function of the filter due to the change in the value of its components. In fact, the sensitivity of the filter transfer function to component values increases as the Q-factor increases. Therefore, to have a stable transfer function over PVT variations, some sort of correction circuitry is required. Two general methods are illustrated in Fig. 2.5 [34, 35]. A filter is placed in a feedback loop and its frequency response is adjusted until it becomes locked to an off-chip stable reference such as a clock frequency,  $f_{\rm ref}$ , as shown in Fig. 2.5(a). If the filtering function cannot be interrupted periodically, two identically constructed on-chip filters may be used in time-interleaved fashion between tuning and system operation [34, 35]. As an alternative approach, a replica of a basic block of the filter is automatically tuned continuously, and the control signal used for that is also applied to the main filter, as shown in Fig. 2.5(b) [34, 35]. This is known as "Master-Slave" technique. Good matching between the filter and the monitor block is an essential requirement for this method. Usually, two parameters of the filter, namely the center frequency and the Q-factor should be corrected in BPFs. A popular method for tuning the Q-factor and the center frequency of the Q-enhanced LC filters is shown in Fig. 2.6 [9, 16, 23, 34, 35]. As can be seen, it is based on an indirect automatic tuning of the filter (Fig. 2.5(b)) and consists of two loops, one for frequency tuning and one for Q-factor tuning.

In summary, current Q-enhanced LC BPF are not suited for RF front-ends applica-

Figure 2.6: A conventional method for tuning the Q-factor and the center frequency of the Q-enhanced LC filters.

tions. However, they can be exploited in the transmitter chain after the up-conversion mixer where the required DR is not demanding [36]. Also in [37], a high-order LC BPF by exploiting high Q-factor bond wires has been implemented which have more than 10 dB of insertion loss. An extensive comparison table is given in [24].

#### 2.3 $G_{m}$ -C BPFs

$G_m$ -C BPFs exhibit inferior performance (e.g., lower DR) compared to the Q-enhanced LC BPFs. This is mainly caused by the fact that in  $G_m$ -C BPFs, an additional active circuitry is needed to synthesize inductors. This leads to more power consumption and less DR compared to Q-enhanced LC BPFs. Moreover, the excess phase-shift of the  $G_m$  cells utilized in these filters, greatly impacts the passband shape and the stability of this type of BPFs.

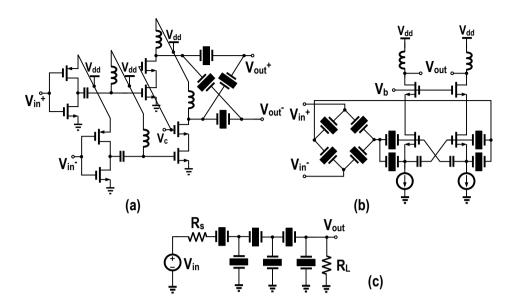

#### 2.3.1 Operation

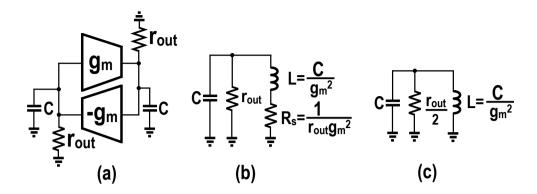

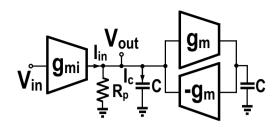

The integrator is the main building block of  $G_m$ -C BPFs which is implemented by a transconductance element loaded with a capacitor. All the state equations of the desired LC BPF prototype can be found and a  $G_m$ -C based integrator can be utilized to synthesize the filter [34, 35]. Another approach which is much easier than the first approach is the utilization of gyrators. It is known that an inductor can be synthesized by a gyrator loaded with a capacitor. Therefore, to design a  $G_m$ -C BPF, we start with a desired LC BPF prototype and substitute all the inductors with its gyrator-based counterpart [35, 38, 39]. The quality of these active inductors determines the attainable maximum center frequency, Q-factor and the DR of this type of filters. Fig. 2.7(a) shows the synthesis of an inductor by a gyrator loaded with a capacitor.

Figure 2.7: (a) An LC resonator where the inductor is synthesized using a gyrator (b) Modeling the active inductor by a lossy passive inductor (c) Its narrow-band approximation.

Figure 2.8: Modeling the extra phase-shift of the G<sub>m</sub> cells by a parallel negative resistance.

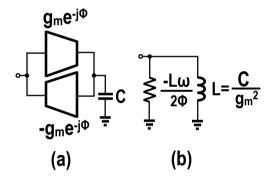

The gyrator is realized by two  $G_m$  cells having a finite output resistance of  $r_{\text{out}}$  connected in a negative feedback. The active inductor can be modeled by a lossy inductor as shown in Fig. 2.7(b). This circuit can be further simplified using narrow-band approximations [25] as illustrated in Fig. 2.7(c). Because the value of active inductor is  $C/g_{\rm m}^2$ , the center frequency of the filter is  $g_{\rm m}/C$ . The Q-factor of the filter is therefore  $Q=0.5g_{\rm m}r_{\rm out}$ , where  $g_{\rm m}r_{\rm out}$  is the DC gain of the  $G_{\rm m}$  cells. In other words, the limited DC gain of the  $G_{\rm m}$  cells puts a fundamental limit on the achievable Q-factor of  $G_{\rm m}$ -C BPFs. It is possible to increase the output resistance of the  $G_{\rm m}$  cells by cascoding [38]. However, this leads to an additional phase-shift due to internal non-dominant poles of the  $G_{\rm m}$  cells. It can be shown that these extra phase-

Figure 2.9: High DC gain  $G_m$  cell: (a) by cascoding which introduces extra non-dominant poles [40] (b) by using negative resistance which does not introduce any extra phase-shift [39].

shifts lead to an additional negative resistance in parallel with the active inductor [38] as illustrated in Fig. 2.8. This effect can be exploited to compensate the loss of the active inductor due to the finite output resistance of the  $G_{\rm m}$  cells. However, the exact modeling of the extra phase-shift due to non-dominant poles is a difficult task. In contrary, an elegant approach to improve the DC gain of the  $G_{\rm m}$  cells has been proposed in [39] where explicit negative resistors are exploited to increase the DC gain of  $G_{\rm m}$  cells without the addition of any undesired poles (Fig. 2.9(b)).

#### 2.3.2 Performance

It can be shown that the DR of a  $2^{\rm nd}$  order  $G_{\rm m}$ -C BPF shown in Fig. 2.10 is described by [14]:

$$DR_{GMC} = \frac{\eta P_{DC}}{8kT(1+\gamma)BQ^2}.$$

(2.5)

In the resonance frequency, the current through the capacitor,  $I_c$ , is Q times larger than the current drawn by the parallel resistance,  $I_{\rm in}$  [25].  $I_c$  should be supplied by the  $G_{\rm m}$  cells making the gyrator. Therefore, the 1-dB output compression power  $P_{\rm 1dB}$  of the filter is limited by the  $G_{\rm m}$  cells making the gyrator. In this way,  $P_{\rm 1dB}$  is Q times lower than the case where a passive inductor is utilized. Moreover, it can be shown that the output noise power of the filter is 2Q times larger compared

Figure 2.10: A 2<sup>nd</sup> order G<sub>m</sub>-C BPF.

Figure 2.11: (a) Combined frequency- and Q-tuning loops [39] (b) Voltage-controlled oscillator for the frequency- and Q-tuning circuit.

to the case of a utilized passive inductor [41]. Interestingly, comparing the dynamic range of  $G_m$ -C BPFs with Q-enhanced BPFs shows that  $G_m$ -C BPFs are  $Q_0^2$  times inferior to Q-enhanced BPFs where  $Q_0$  is the Q-factor of on-chip inductors. Due to this fundamental superiority of Q-enhanced BPFs over  $G_m$ -C BPFs, logically, all the published GHz range integrated active BPFs are based on Q-enhanced LC filters.

It is possible to mitigate the effect of Q-factor on the output noise of the filter simply by increasing the size of the capacitors by Q. To achieve the same center frequency as before, all the  $G_m$  cells should be scaled up Q times ( $\omega_0 = g_m/C$ ). This directly translates to Q times increase in the power consumption of the filter. Also as the center frequency,  $\omega_0$ , of the filter increases, the required value of the  $G_m$  cells should be increased proportionally ( $g_m \propto \omega_0 Q$ ). As a consequence, the current consumption of the filter is directly proportional to the product of the center frequency,  $\omega_0$ , and the Q-factor of the filter.

#### 2.3.3 Frequency Response Stability

The sensitivity of  $G_m$ -C BPFs to process variations is higher than Q-enhanced LC BPFs. In general, two explicit feedback loops are required to correct the center

Figure 2.12: Configurations of BAW resonators: (a) Surface micro-machined FBAR (film bulk acoustic resonator) (b) SMR (solidly mounted resonator).

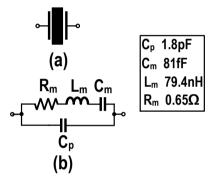

Figure 2.13: (a) A symbol of a resonator (b) An RLC modeling of a resonator; component values for a FBAR resonator also are given [43].

frequency and Q-factor of the filter [39, 42]. The frequency and Q-factor control loops that have been used in [39] are shown in Fig. 2.11.<sup>2</sup>

#### 2.4 Micro-Mechanical Filters

One approach to the miniaturization of transceivers is to explore the possibility of integration of passive high-Q resonators. There are two distinct directions in this approach. The first one is the exploitation of CMOS compatible piezoelectric materials such as AlN. The second direction is the utilization of capacitive-transduction MEMS structures which are quite friendly with CMOS processing and provide us with very high Q-factors even in the air. In this section, we will give a summary of both directions.

<sup>&</sup>lt;sup>2</sup>In reality, the amplitude detector and control loop were built inside the VCO to prevent a possible instability due to the interaction of the Q-factor and  $f_c$  loops.

Figure 2.14: (a) Using a lattice filter in PA to filter out undesired signals [52] (b) Utilizing a double lattice configuration before LNA [50, 53] (c) Ladder BPF based on FBAR resonators [54].

#### 2.4.1 Piezoelectric Resonators

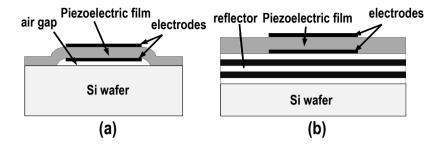

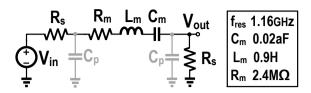

The basic configuration of a BAW (Bulk Acoustic Wave) resonator is a piezoelectric thin film surrounded by two metal electrodes [43, 44, 45, 46, 47, 48, 49, 50, 51, 52]. Fig. 2.12 shows the two main configurations for realizing BAW resonators. The first resonator, also known as a film bulk acoustic resonator (FBAR), is a membrane structure suspended in the air by its edges. The second configuration is the solidly mounted resonator (SMR), in which the acoustic impedance of the substrate is transformed to a very low value to reduce the energy loss through the substrate and hence sustaining the high Q-factor of the resonator. In comparison with surface acoustic wave (SAW) devices, BAW resonators and filters exhibit a lower frequency drift with temperature [50]. The FBAR resonator can be modeled electrically as a series RLC circuit in parallel with a capacitor. This model is shown in Fig. 2.13 [43]. FBAR resonators can offer Q-factors in the range of 1k [43, 44, 45, 46, 47, 48, 49, 50, 52, 53]. In [43], a duplexer based on FBAR resonators was fabricated working at 1900 MHz (the PCS band), which was 10 times smaller than its off-chip counterpart and it was better than a SAW duplexer in terms of power handling [46, 47, 48].

In general, utilization of high-Q resonators leads to a considerable reduction in the power consumption of the receivers[55, 56, 57]. FBAR resonators are extensively used in oscillator design leading to very low power and low phase-noise LO generations [43, 44, 45, 49, 53, 56, 58, 59]. In most cases, the FBAR resonators are wire bonded to the transistor chip. However, in [44], the resonator is directly integrated above the IC which leads to the reduction in the area. One of the issues of oscillators exploiting high-Q resonators is the limited tunability of this type of resonators which is mainly due to the inherent parallel capacitance of the resonators. In [45], a technique has been proposed to cancel this parallel capacitance. Here, some examples where the FBAR resonators have been utilized to design high-order BPFs will be discussed. In [52], A high-Q BAW lattice BPF was co-designed with a power amplifier as shown in Fig. 2.14(a). In [50, 53], a double lattice BPF before the LNA was exploited to relax the linearity requirement of the LNA and reduce its power consumption. The exploited double lattice configuration is shown in Fig. 2.14(b). Also, a ladder filter [22] based on FBAR resonators is shown in Fig. 2.14(c) [54]. BPFs based on FBAR resonators are the best options from DR and power consumption points of view. However, there are some issues associated with them that need to be addressed. One is the accuracy of the resonance frequency of the FBAR resonators. The resonance frequency of the FBAR resonators is inversely proportional to the thickness of the piezoelectric material. Although the lateral dimensions can be made quite accurate in the fabrication process (it is limited by the lithography.), the thickness of the layers are not very well controlled. This can potentially lead to a deviation in the center frequency of the resonators and filters [53]. Another issue is that they are not tunable. Therefore, to cover different frequency bands, a large arrays of them would be necessary that definitely increases the area and cost.

#### 2.4.2 Capacitive-Transduction Resonators

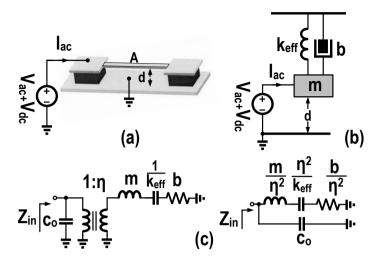

There has been tremendous research on capacitive-transduction resonators due to their high compatibility with CMOS fabrication processes and their simplicity [60, 61, 62, 63, 64, 65, 66, 67, 68, 69, 70, 71, 72, 73, 74, 75, 76]. This has led to a large number of different structures for this type of resonators. In [62], it is proposed to exploit the mechanical nonlinearity of the resonator to achieve a Mixer-Filter ("Mixler"). Moreover, in [77], an interesting idea of resonant-gate transistor has been proposed which operates as a frequency-selective transistor.

Now, a brief explanation of how this type of resonators are operating, will be given. A simplified clamped-clamped beam resonator which is stimulated by an input voltage of  $V_{DC} + V_{ac}$  is illustrated in Fig. 2.15(a) where  $V_{ac} \ll V_{DC}$ . Using its simplified lumped spring-mass model shown in Fig. 2.15(b), its input impedance can be calculated [61]. The input impedance of the resonator consists of two parts, a

$<sup>^3</sup>$ In other words,  $V_{\rm DC}$  sets the mechanical DC point and  $V_{\rm ac}$  acts like a small-signal perturbation around that point (similar to what we do in small signal analysis of transistors).

Figure 2.15: (a) A clamped-clamped beam resonator (b) A simplified lumped model of the resonator (mass-spring) (c) Equivalent input impedance of the resonator;  $\eta$  is the electrical to mechanical transduction.

series RLC tank and a parallel capacitance as illustrated in Fig. 2.15(c). The input impedance of the filter is:

$$Z_{in}(s) = \left(L_{m}s + \frac{1}{C_{m}s} + R_{m}\right) \left\| \frac{1}{C_{o}s} \right\}$$

$$L_{m} = \frac{m}{\eta^{2}}, C_{m} = \frac{\eta^{2}}{k_{eff}}, R_{m} = \frac{b}{\eta^{2}}, C_{m} = \frac{\epsilon A}{d}$$

$$(2.6)$$

where A is the area of the resonator, d is the distance between the two plates of the resonator,  $\epsilon$  is the permeability of the dielectric between the two plates,  $k_{\rm eff}$  is the effective stiffness of the resonator, m is its mass, b is the damping factor of the resonator, and  $\eta$  is the electrical-to-mechanical transduction of the resonator which is approximately  $\epsilon AV_{DC}/d^2$ . The series resonance frequency and Q-factor of the resonator can be found by:

$$\omega_{\rm o} = \sqrt{\frac{k_{\rm eff}}{\rm m}}$$

$$Q = \frac{\sqrt{\rm m}k_{\rm eff}}{b}$$

(2.7)

It can be shown that the stiffness of the resonator is not constant and it has a nonlinear relationship with the applied DC voltage,  $V_{\rm DC}$ , as described by:

Figure 2.16: (a) Lowering the impedance level of the resonator by exploiting a large number of them in parallel (b) In ideal case, by paralleling n resonators, the input admittance of the resonator increases by n times; however, in reality due to the mismatch, this is not the case.

$$k_{\text{eff}} = k - \frac{\epsilon A V_{\text{DC}}^2}{2(d - x_0)^3}$$

$$(2.8)$$

where  $x_0$  is the DC displacement point of the resonator. Interestingly, as  $V_{DC}$  increases, the effective stiffness of the resonator,  $k_{eff}$ , decreases. It is possible to exploit this property to tune the center frequency of the resonators. The tuning range is severely limited and practical achieved results show a tuning range of  $\ll 1\%$ . There is a specific input DC voltage  $(V_{pull-in})$  and a DC displacement point  $(x_{pull-in})$  (2.9) where  $k_{eff}$  will be zero and consequently the two plates of the resonator will stick to each other [61]. The dependence of the effective stiffness,  $k_{eff}$ , to the applied voltage (2.8) is the source of nonlinearity in the capacitive-transduction resonators leading to a worse linearity performance compared to SAW filters [68].

$$x_{\text{pull-in}} = \frac{d}{3}$$

$$V_{\text{pull-in}} = \sqrt{\frac{8d^3k}{27\epsilon A}}$$

(2.9)

One of the main issues of the capacitive-transduction resonators is their very large impedance level (e.g., 791 k $\Omega$  at  $f_{\rm res}=1.5$  GHz) compared to resonators based on piezoelectric materials (e.g., 0.65  $\Omega$  at  $f_{\rm res}=2$  GHz) [60, 61, 62, 63, 64, 65, 66, 67, 68, 69, 70, 71, 72, 73, 74, 75, 76]. One way to reduce the impedance level of these resonators is to exploit a large number of them in parallel as shown in Fig. 2.16(a). However, there is a big challenge in this approach. Due to the variations in the fabrication process and the high Q-factor of the resonators, it is quite difficult to add all the signals from all the paths in a constructive way as illustrated in Fig. 2.16(b). Alternatively, as can be seen from (2.6), increasing  $\eta = \epsilon AV_{\rm DC}/{\rm d}^2$  will reduce

Figure 2.17: A 2<sup>nd</sup> order BPF based on a MEMS resonator where the equivalent RLC values of a MEMS resonator [64] are given as an example.

the input impedance of the filter. There are different possibilities: 1) increasing the area of the resonator, A; 2) reducing the gap distance, d; 3) Using dielectric materials with high permeability,  $\epsilon$ ; and 4) increasing the DC bias voltage of the resonator,  $V_{DC}$ . Reducing the gap distance, d, has the most significant impact on lowering the input impedance of the resonator,  $R_{\rm m} \propto 1/d^4$ . According to [68], all of these options lead to a degradation in the linearity performance of the resonator.<sup>4</sup> Therefore, fundamentally, capacitive-transduction MEMS resonators suffer from a trade-off between their impedance-level and linearity.

The different types of capacitive-transduction resonators with a summary of their structures, frequency range, Q-factors, and motional resistances,  $R_m$ , are illustrated in Table 2.1. As can be seen, very high Q-factors even in the air is possible in GHz range frequencies. The motional impedance of the MHz range MEMS resonators is in range of  $8-40~\text{k}\Omega$ . Currently, high-performance low-frequency oscillators based on MEMS resonators are commercially available [80]. However, the motional impedance of GHz range MEMS resonators is in M $\Omega$  range. A 2<sup>nd</sup> order BPF based on a MEMS resonator is illustrated in Fig. 2.17 where the equivalent RLC values of a MEMS resonator [64] are given as an example. It can be shown that the S<sub>21</sub> of the filter is:

$$S_{21} = \left(1 + \frac{R_{\rm m}}{2R_{\rm s}}\right)^{-2} \tag{2.10}$$

which can be simplified to  $(2R_s/R_m)^2$  for  $R_m \gg R_s$ . Therefore, high motional impedance,  $R_m$ , can lead to a notoriously low  $S_{21}$  (e.g., -80 dB in a  $50~\Omega$  environment [64]). According to (2.10), for a constant  $R_m$ , it is possible to increase  $S_{21}$  by increasing the value of the source and load resistance,  $R_s$ . However, the amount of improvement is limited at high frequency due to the presence of parasitic capacitors,  $C_p$ , as shown in Fig. 2.17.

In summary, currently low-frequency MEMS resonators are quite suitable for lownoise oscillator design having smaller form-factors compared to crystal oscillators [80].

$<sup>^{4}</sup>$ This also can be seen by the fact that all the mentioned techniques lead to a reduction in the  $V_{\text{pull-in}}$  of the resonator (2.9) which is a fair measure of the nonlinearity of the resonator.

Table 2.1: Summary of different capacitive-transduction MEMS resonators

| Device       | Configuration                                                                                                            | Q                                                                              | $R_m(k\Omega)$                                    |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------|--|

| CC beam [61] | W <sub>r</sub> = 8 µm                                                                                                    | 8000 @10MHz(vac.)<br>50 @10MHz(air)<br>300 @70MHz(vac.)<br>Limited freq. range | 8.7 @54.2MHz<br>35.2 @71.8MHz                     |  |

| FF beam [78] | Drive Counter-Wavelength Torsland Beam 1µm 14.3µm 14.3µm Flexural-Mode Ground Plane and Sense Electrode                  | 20k @10-200MHz(vac.)<br>2k @90MHz(air)<br>Wide freq. range                     | 31.1 @31.51MHz<br>10.7 @50.35MHz<br>167 @92.25MHz |  |

| WG disc [76] | Anchor Wine Glass Output Disk Resonator Output $R = 32 \text{ µm}$ Output $C = 30 \text{ nm}$ Support Input Anchor Beams | 156k @60MHz(vac.)<br>8k @98MHz(air)<br>Wide freq. range                        | 176 @425.3MHz<br>200 @1500MHz                     |  |

| CM disc [64] | Blas Electrode  R= 6.3 µm   Support Ribbing                                                                              | 11.5k @1.5GHz(vac.)<br>10.1k @1.5GHz(air)<br>Wide freq. range                  | 480 @151.3MHz<br>2422 @1156MHz                    |  |

| HD ring [79] | Anchor Stam Support Beam Drive Electrode  V. Sense Electrode  T. V. Sense Electrode                                      | 11.5k @1.5GHz(vac.)<br>10.1k @1.5GHz(air)<br>Wide freq. range                  | 480 @151.3MHz<br>2422 @1156MHz                    |  |

| WG ring [70] | Port 7  Port 7  Port 3  R <sub>outer</sub> =28,2 <sub>jun</sub> Port 3  Port 5                                           | 3k @1.5GHz(air) 7.7k @210MHz(air) Wide freq. range                             | 600 @634MHz<br>791 @1.5GHz                        |  |

Figure 2.18: A general N-path (a) BPF (b) BSP.

However, RF frequency capacitive-transduction MEMS filters, having  $S_{21} < -80 \text{ dB}$ , seem to be not viable options for RF filtering.

#### 2.5 N-path Filters

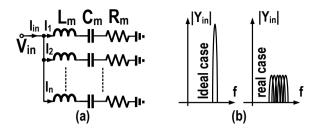

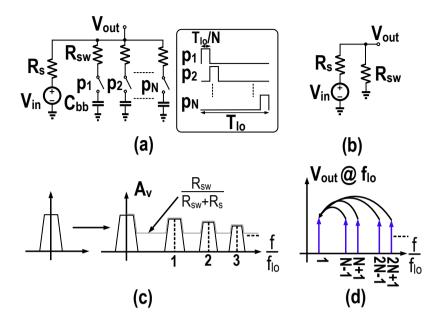

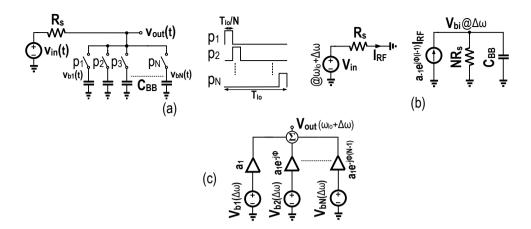

N-path filtering is an old technique [81, 82, 83, 84, 85, 86, 87, 88, 89, 90, 91] (Fig. 2.18). The oldest N-path filter (at that time, it was called "commutated networks") seems to be [81] which was published in 1953. A center-frequency tunable switched-RC BPF and a band stop filter (BSF) were proposed in [81]. Interestingly, at that time, the switches were made mechanically due to the lack of transistors. The general idea of Npath filtering is simple. Instead of filtering the signal at RF, it is first downconverted to baseband by exploiting the first set of switches that operates as a mixer. Afterwards, these down-converted signals are lowpass (highpass) filtered due to the LP(HP) filters. Eventually, these filtered signals are upconverted again to the RF frequency. This procedure can be interpreted as a transformation of a LP(HP) filter to a BP(BS) filter around the switching frequency. This idea is usually very helpful because the design of LP(HP) filters is much easier than the design of BP(BS) filters. A timedomain analysis of general N-path filters has been presented in [82, 83, 85, 87, 89, 90] and a frequency-domain analysis of N-path filters was introduced in [83]. The first integrated N-path filters were demonstrated in [84, 86, 91]. The N-path technique was utilized in switched-capacitor filters extensively [87, 92, 93, 94]. At that time, the two main obstacles in the implementation of integrated N-path filters were: 1) the achievable matching between the different paths of the N-path filters, which is crucial for the proper operation of the filter, was not good enough [88]; and 2) the maximum achievable switching frequency of the integrated circuits was quite low. These two main issues reduced the attention of researchers for N-path filters. The substantial improvement in the speed and the matching properties of CMOS technology renewed a great interest into N-path filters [95, 96, 97, 98, 99, 100, 101, 102, 103, 104, 105]. Because the main constituents of N-path filters are switches and capacitors, CMOS

Figure 2.19: (a) An N-path BPF [81] (b) A simplified schematic of the filter for outof-band frequencies (c) Transformation of a LPF to BPFs at different harmonics of the clock frequency,  $f_{lo}$ ; non-zero  $R_{sw}$  limits the stopband rejection of the filter (d) Folding-back of Signals located at  $|kN-1|f_{lo}$  to  $f_{lo}$ .

technology is the best candidate for the realization of this type of filters.

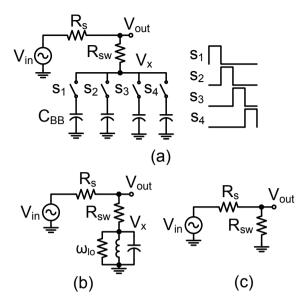

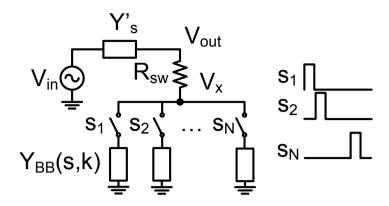

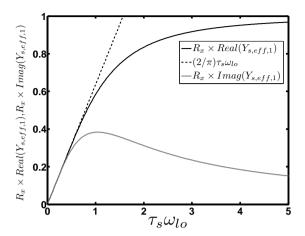

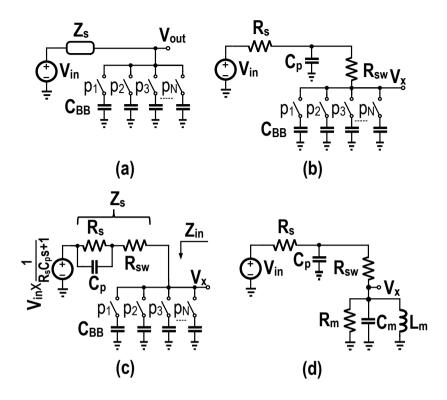

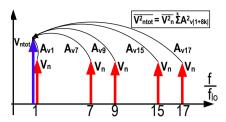

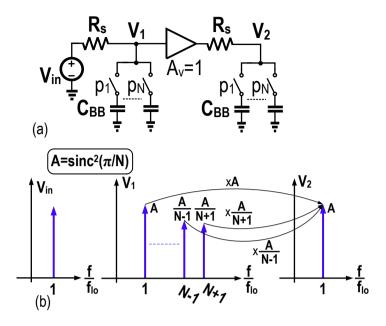

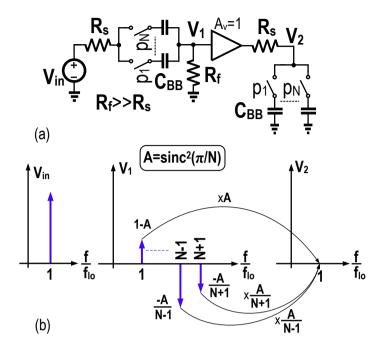

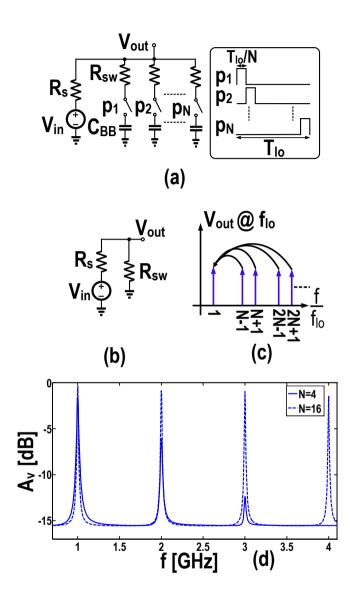

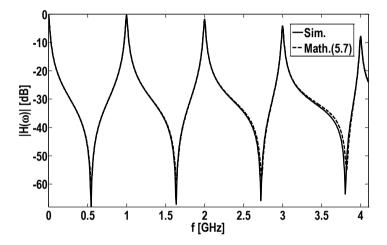

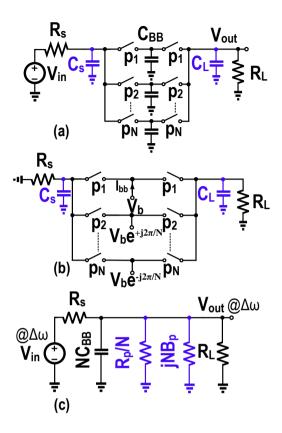

An N-path BPF [81] that has recently attracted much attention [95, 96, 97, 98, 99, 101, 102, 103, 104, 105] is illustrated in Fig. 2.19(a) where the on-resistance of the switches is modeled by a series resistance,  $R_{sw}$ . The clock signals,  $p_i(t)$  i = [1, N], are non-overlapping clocks with a duty cycle of 1/N. The input RF signals located around the m<sup>th</sup> harmonics of the clock frequency,  $mf_{lo}$ , will be downconverted to baseband due to the switching operation of the switches. These baseband signals are then filtered due to the lowpass filtering of the combination of baseband capacitors,  $C_{bb}$ , and the source resistance,  $R_s$ . Due to the transparency of the switches, these lowpass filtered baseband signals will be upconverted to around  $mf_{lo}$ . This procedure can be interpreted as a transformation of a LPF, which consists of  $C_{bb}$  and  $R_s$ , to BPFs centered at different harmonics of  $f_{lo}$ . The LPF to BPF transformation is illustrated in Fig. 2.19(c). In this way, N-path filters provide us with center-frequency tunable BPF where the bandwidth of the filter can be chosen independent of the center frequency by the value of C<sub>bb</sub>. There are some issues associated with N-path filters, namely: 1) limited stopband rejection due to the non-zero switch resistance,  $R_{sw}$ ; 2) undesired folding-back of the signals located at  $|kN-1|f_{lo}$  to the center frequency of the filter,  $f_{lo}$  (Fig. 2.19(d)); and 3) the repetition of the bandpass shapes at higher harmonics of the clock frequency. For frequencies far from the passband of the filter, the impedance of the baseband capacitors,  $C_{bb}$ , is negligible and can be ignored. In this way, the filter can be simplified to a resistive divider shown in Fig. 2.19(b). As a consequence, the ultimate-rejection of the filter is limited to  $R_{sw}/(R_{sw} + R_s)$  as depicted in Fig. 2.19(c) [98].

#### 2.6 Conclusion

The trend towards reconfigurable radio transceiver architectures asks for BPFs with good selectivity and a flexibly tunable center frequency. The off-chip available solution is to use an array of dedicated, bulky, off-chip and non-tunable filters such as SAW filters. Although BAW filters [53] have been introduced as a system in package solutions, their center frequency is sensitive to the thickness variation of the piezoelectric material and the achievable tunability is quite limited [53]. If they are used for reconfigurable receivers, an array of them is necessary which again leads to the usage of a considerable amount of area. On the other hand, there are several techniques to make integrated RF BPFs such as LC filters [14, 20, 21], often with Q-enhancement techniques, G<sub>m</sub>-C filters [9, 14, 42], N-path filters [83, 87, 92, 93, 94, 103]. LC filters have several disadvantages such as high area consumption due to inductors which do not obey process scaling and have low quality factor, limited tunability and poor dynamic range [14, 20, 21]. The main drawbacks of  $G_m$ -C filters are the tradeoffs among power consumption, quality factor, center frequency and dynamic range and the need for tuning circuitry [14, 42]. On the other hand, N-path filters have interesting features such as direct tunability with  $f_{lo}$ , potentially higher Q-factors compared to the on-chip CMOS LC filters, high linearity and graceful scaling with process.

According to [14], the DR of  $G_m$ -C filters depends on  $1/Q^2$  while the DR of the Q-enhancement filters depends on  $Q_0^2/Q^2$  where  $Q_0$  is the quality factor of onchip inductors.  $G_m$ -C filters need extra circuitry (gyrators) to synthesize inductors and Q-enhancement filters require extra circuitry (a negative impedance) to enhance the Q-factor of on-chip inductors and these extra circuitries lead to a lower DR. However, in the N-path technique, the required Q-factor of the filter can be obtained by increasing  $C_{\rm bb}$  ( $Q \propto C_{\rm bb}(R_s + R_{sw})$ ) and no extra active devices are needed. Therefore, essentially, the Q-factor of the N-path filters is decoupled from its DR. Therefore, the focus of this thesis is on the design and implementation of N-path filters.

## Chapter 3

# Tunable Switched G<sub>m</sub>-C Bandpass Filter Based on N-path Filters

#### 3.1 Introduction

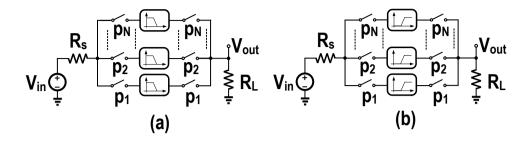

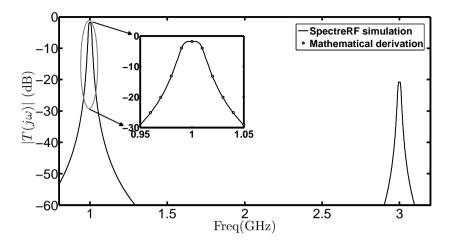

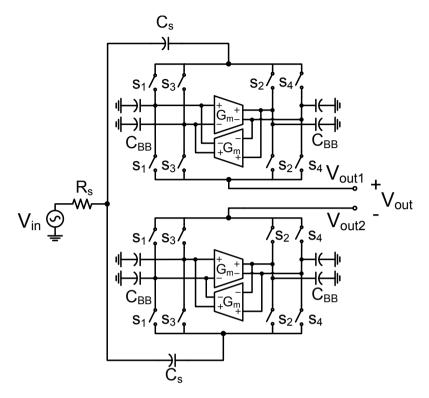

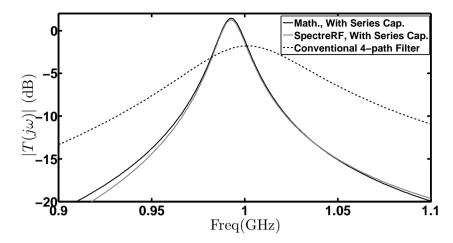

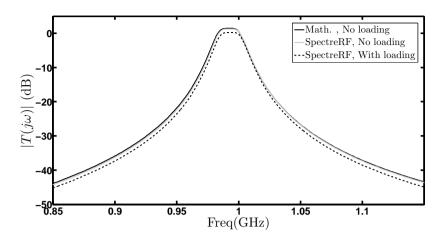

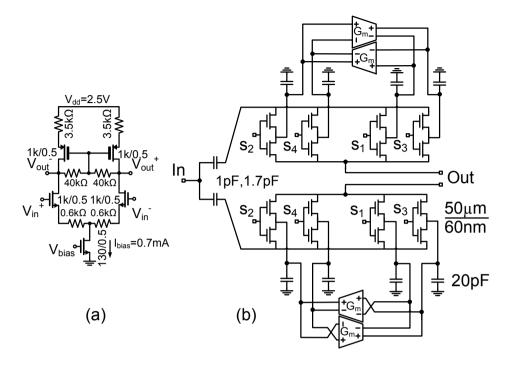

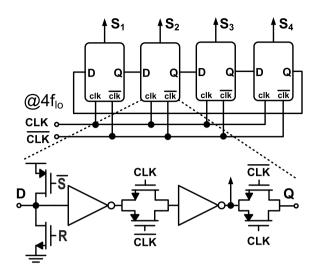

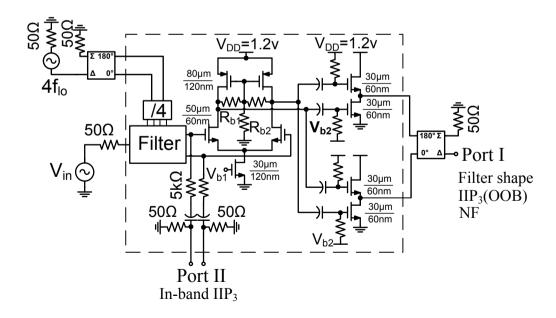

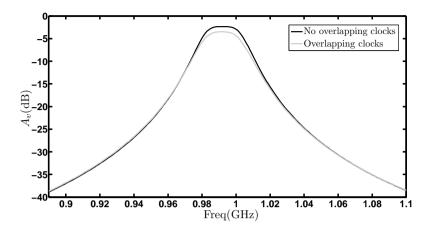

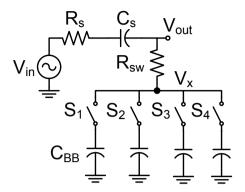

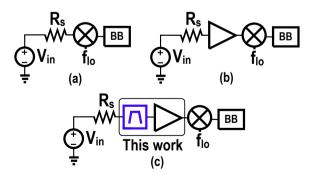

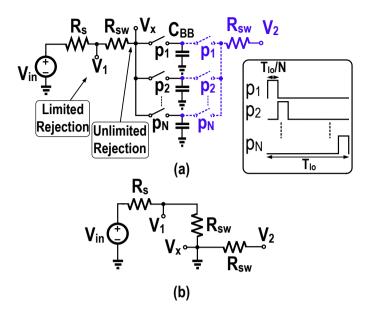

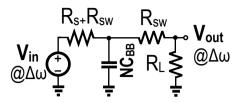

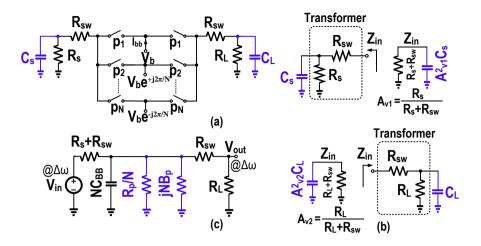

As discussed in chapter 2, the trend towards reconfigurable radio transceiver architectures asks for BPFs with good selectivity and a flexibly tunable center frequency. As concluded in chapter 2, N-path filters are the best candidate for this purpose. A 4-path filter with capacitive baseband impedances and its LTI (Linear Time Invariant) equivalent around  $f_{lo}$  are depicted in Fig. 3.1(a) and Fig. 3.1(b), respectively [19, 96, 97, 101, 102, 106]. At frequencies far from  $f_{lo}$ , the baseband capacitors will be shorted to ground and thus the filter will be simplified to a simple resistive division between source resistance  $R_s$  and switch resistance  $R_{sw}$  [96] (Fig. 3.1(c)). N-path filters have two main limitations: 1) the switch resistance  $R_{sw}$  limits the ultimate rejection to  $R_{sw}/(R_{sw}+R_s)$  where  $R_s$  is the source impedance (16 dB for  $R_s=50~\Omega$ and  $R_{sw} = 10 \Omega$ ) [19, 96, 107]; 2) recently published N-path filters have only second order filtering, and higher orders have only been achieved by cascading [103], still rendering a "round" bandpass filter shape. In this chapter, a new method to increase the order of the bandpass filter while having a better passband shape compared to [103, 106] is proposed [99]. The introduced technique, also weakens the effect of the switch-resistance on the ultimate rejection obtaining > 55 dB ultimate rejection in a 65 nm LP CMOS chip.

The outline of this chapter is as follows: In section 3.2, the idea of subtraction as a method to obtain a 4<sup>th</sup> order BPF from two 2<sup>nd</sup> order BPFs with different center

Figure 3.1: (a) A conventional 4-path filter (b) its LTI equivalent around  $f_{lo}$  and (c) equivalent circuit for evaluating the ultimate rejection.

frequencies will be introduced. Subsequently, in section 3.3 the idea of shifting the center frequency of a 4-path filter upward and downward exploiting a switched  $G_m$ -C technique will be discussed. Moreover, we discuss how the frequency shifts are implemented using a switched  $G_m$ -C technique. Consequently, utilization of this idea into the subtraction circuit, will be discussed. In Section 3.4, signal splitting to supply the input voltage signal to the two shifted 4-path  $2^{nd}$  order BPFs and its effect on the resultant filter will be discussed. Section 3.5 and 3.6 discuss the filter realization and measurements, respectively. In section 3.7, conclusions will be drawn.

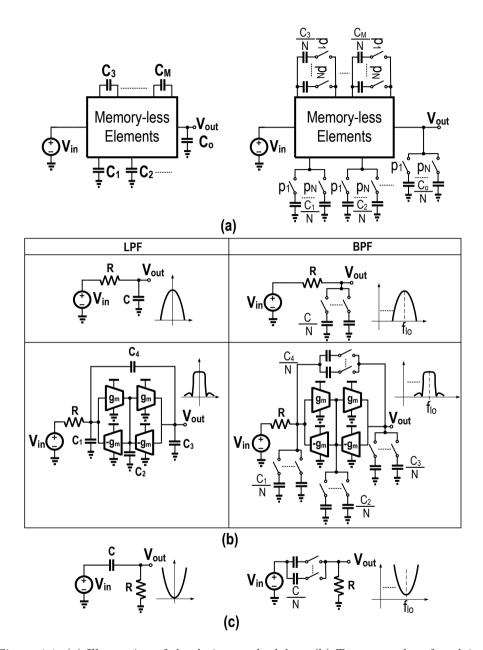

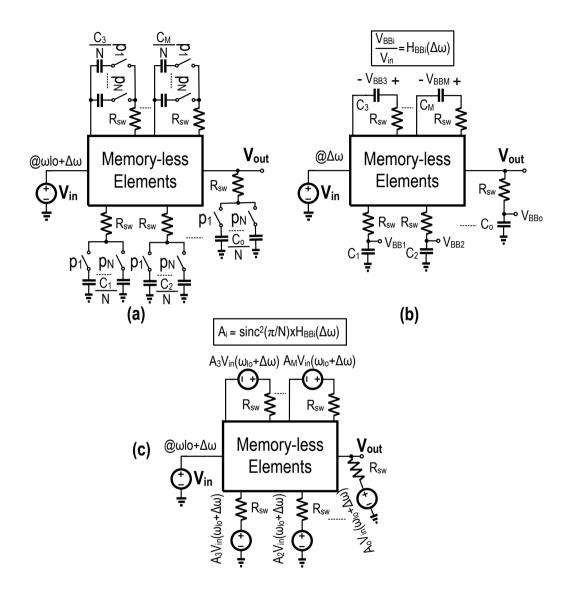

## 3.2 Increasing BPF Order By Subtraction

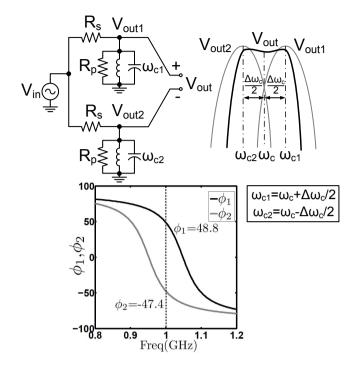

We propose to use subtraction as a means to achieve a 4<sup>th</sup> order BPF from the two 2<sup>nd</sup> order BPFs with slightly different center frequencies. The main idea is illustrated in Fig. 3.2. Intuitively, the relation between the phase of  $V_{\text{out}1}$  and  $V_{\text{out}2}$  ( $\phi_1$  and  $\phi_2$ ) is approximately  $\phi_1 = -\phi_2$  in the pass-band of the resultant filter and therefore due to the subtraction, they will add up. However, for frequencies far out of the pass-band region of the resultant filter, the signals in the 2 paths are almost in-phase  $\phi_1 = \phi_2$  and will cancel each other. Mathematically, the transfer function of each path in Fig. 3.2 is:

Figure 3.2: Obtaining a 4<sup>th</sup> order BPF based on the subtraction of two 2<sup>nd</sup> order BPFs with slightly different center frequencies; the relation between the phase of each path  $(\phi_1,\phi_2)$ : in the pass-band of the resultant filter is approximately  $\phi_1 = -\phi_2$  and for frequencies far out of the pass-band region of the resultant filter, the signals in the 2 paths are almost in-phase  $(\phi_1 = \phi_2)$ .

$$H_{i}(s) = \frac{V_{\text{out},i}(s)}{V_{\text{in}}(s)} = \frac{R_{p}}{R_{s} + R_{p}} \times \frac{\omega_{3\text{dB},i}s}{s^{2} + \omega_{3\text{dB},i}s + \omega_{ci}^{2}} i = 1, 2$$

(3.1)

where  $\omega_{ci}$  and  $\omega_{3\text{dB},i}$  are center frequencies and bandwidths of the two paths. If the bandwidth of each path is the same ( $\omega_{3\text{dB},1} = \omega_{3\text{dB},2} = \omega_{3\text{dB}}$ ) and assuming that  $\omega_{c1} = \omega_c + 0.5\Delta\omega_c$  and  $\omega_{c2} = \omega_c - 0.5\Delta\omega_c$ , the total transfer function of the resultant filter will be:

$$H(s) = \frac{V_{\text{out}}(s)}{V_{\text{in}}(s)} = \frac{R_p}{R_s + R_p} \times \frac{2\omega_{3\text{dB}} \times \omega_c \times \Delta\omega_c \times s}{\left(s^2 + \omega_{3\text{dB}}s + \omega_{c1}^2\right)\left(s^2 + \omega_{3\text{dB}}s + \omega_{c2}^2\right)}.$$

(3.2)

Now, we want to synthesize a 4<sup>th</sup> order BPF which has a bandwidth of BW(Hz) and is centered at  $\omega_c$ . Let us assume that the desired LPF prototype is  $k/(s^2+as+b)$ .

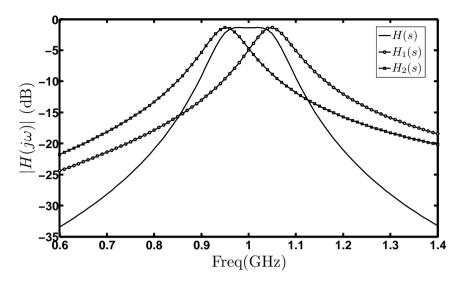

Figure 3.3: A 4<sup>th</sup> order BPF centered at  $f_c=1$  GHz with BW = 124 MHz and 0.05 dB ripple ( $a=0.7,\ b=0.27$ ) centered at 1 GHz as a result of the subtraction of two 2<sup>nd</sup> order BPFs with bandwidths of 87 MHz centered at  $f_{c1}=1.05$  GHz and  $f_{c2}=0.95$  GHz ( $R_s=50\ \Omega$  and  $R_p=300\ \Omega$ ).

For this purpose, the values needed for  $\Delta\omega_c$  and  $\omega_{3\text{dB}}$  are  $2\pi\text{BW} \times \sqrt{4b-a^2}$  and  $2\pi\text{BW} \times a$ , respectively. For example, by subtracting the outputs of two 2<sup>nd</sup> order BPFs with bandwidth of 87 MHz centered at  $f_{c1}=1.05$  GHz and  $f_{c2}=0.95$  GHz, a 4<sup>th</sup> order BPF centered at  $f_c=1$  GHz with 0.05 dB ripple and bandwidth of 124 MHz will result (Fig. 3.3).

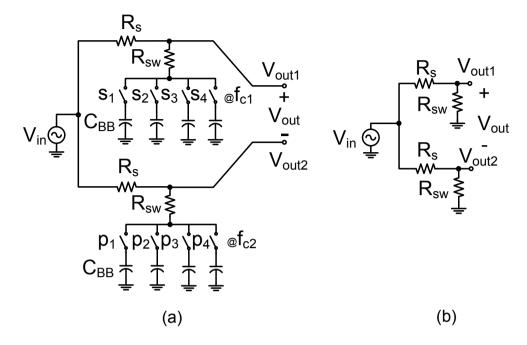

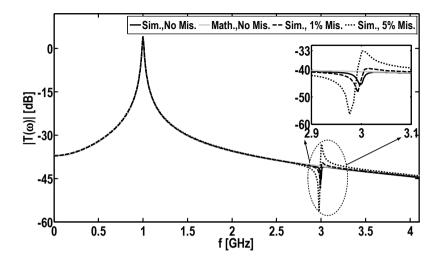

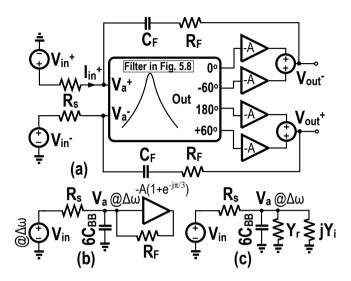

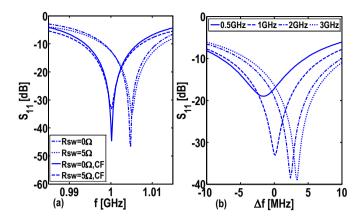

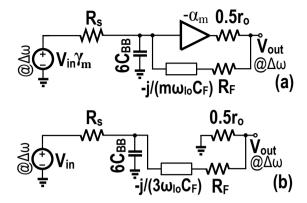

Each RLC tank in Fig. 3.2 can be replaced by a 4-path passive-mixer filter with different clock frequencies ( $f_{c1}$  and  $f_{c2}$ , one for each path). In this way, a tunable 4<sup>th</sup> order BPF can be made (Fig. 3.4(a)). Another property of this filter is that it can improve the limited ultimate rejection of conventional N-path filters. The filter shown in Fig. 3.4(a) will reduce to Fig. 3.4(b), for input frequencies far from the center frequency of the filter. In the case of no mismatch in the subtraction and the switch resistance values of upper and lower paths, the ultimate rejection will be infinite ( $R_{sw}/(R_{sw}+R_s)-R_{sw}/(R_{sw}+R_s)=0$ ). In case of switch resistance mismatch  $\Delta R_{sw}$  between upper and lower path, the ultimate rejection will be limited to  $\Delta R_{sw}/(R_{sw}+R_s)$ . Compared to the ultimate rejection of conventional N-path filters, a great improvement has been introduced. For example for a 1% mismatch between the switch resistance values of the upper and lower path and assuming  $R_{sw}=10~\Omega$  and  $R_s=50~\Omega$ , the ultimate rejection will be 55 dB compared to 16 dB ultimate rejection of conventional N-path filters. A disadvantage of the filter shown in Fig.

Figure 3.4: (a) A  $4^{\rm th}$  order tunable BPF using two different clock frequencies and (b) equivalent circuit to find the ultimate rejection

3.4(a) is the need for a complicated clock circuitry. Instead, an alternative way is proposed to realize the filter with just one clock frequency which is discussed in section 3.3.

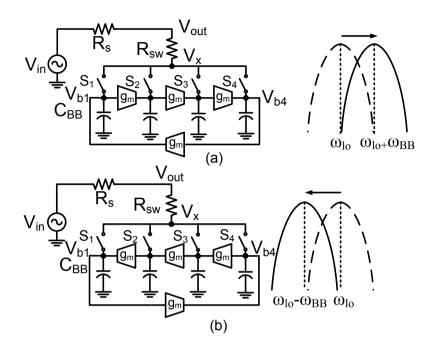

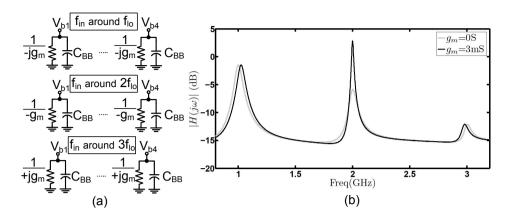

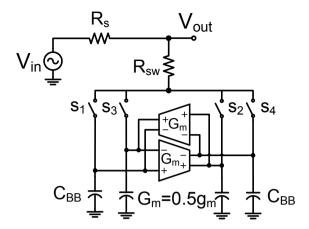

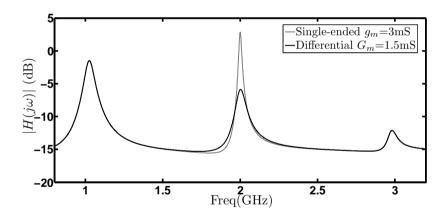

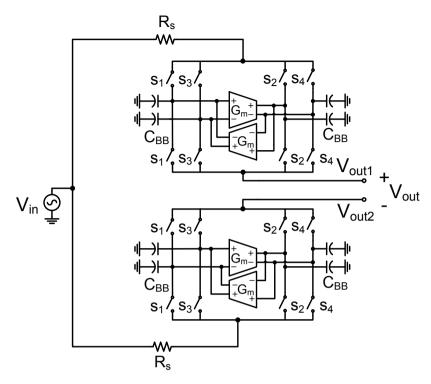

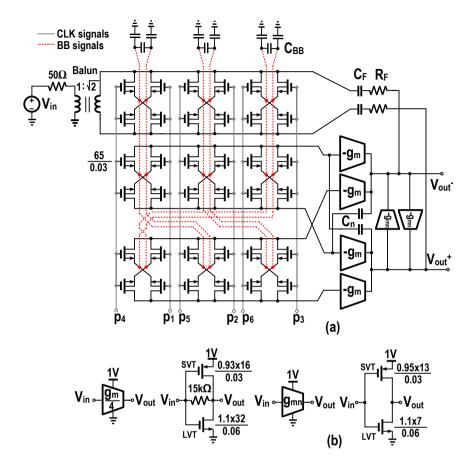

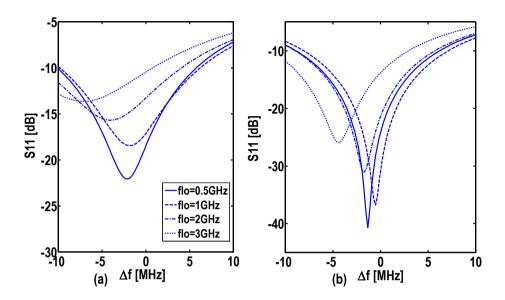

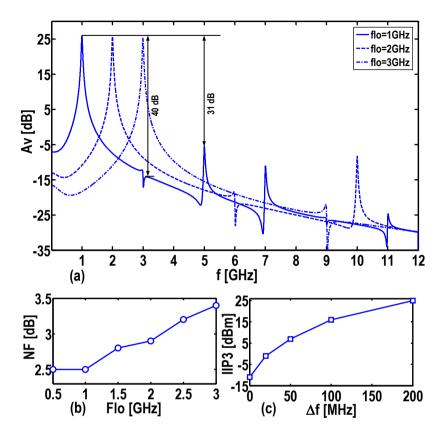

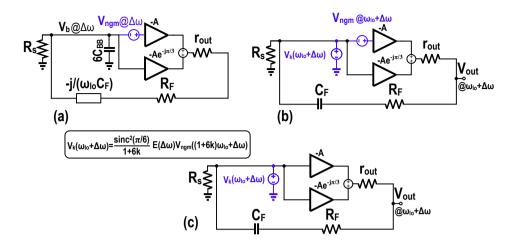

### 3.3 Shifting the center frequency of a 4-path filter